## 前回の講義の復習(1)

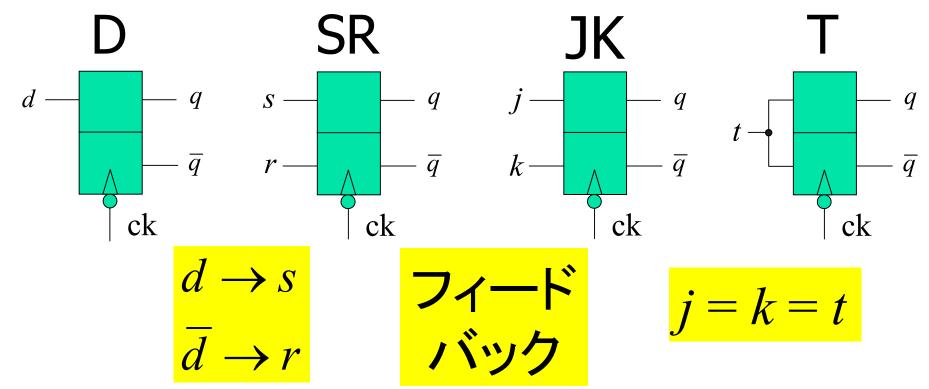

フリップフロップ

## 前回の講義の復習(2)

クロックパルス (ck) 入力 (d, s, r, j, k, t) 必要

り フリップフロップの駆動回路

| $q_i$ | $q_i^{(1)}$ | $d_{i}$ | $S_{i}$ |   | $j_i$ | $k_{i}$ | $t_i$ |

|-------|-------------|---------|---------|---|-------|---------|-------|

| 0     | 0           | 0       | 0       |   |       | *       |       |

| 0     | 1           | 1       | 1       | • | 1     | *       | 1     |

| 1     | 1           | 1       | *       | 0 | *     | 0       | 0     |

| 1     | 0           | 0       | 0       | 1 | *     | 1       | 1     |

|       | $q^{(1)}$ |   |  |  |  |

|-------|-----------|---|--|--|--|

| $q^t$ | 0         | 1 |  |  |  |

| 0     | 0         | 1 |  |  |  |

| 1     | 1         | 0 |  |  |  |

(1)

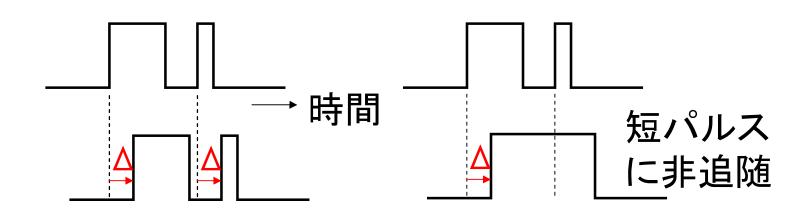

## 回路の遅延

- ■純粋遅延(タイミング調整)

- ■浮遊遅延(論理素子や配線に付随)

純粋遅延

浮遊遅延

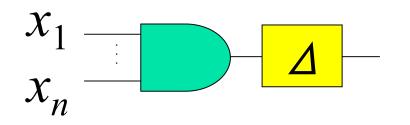

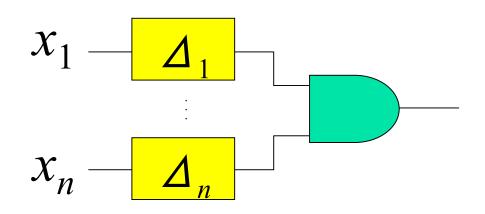

## 論理素子の遅延モデル

出力遅延型 (TTL)

入力遅延型 (MOS,VLSI)

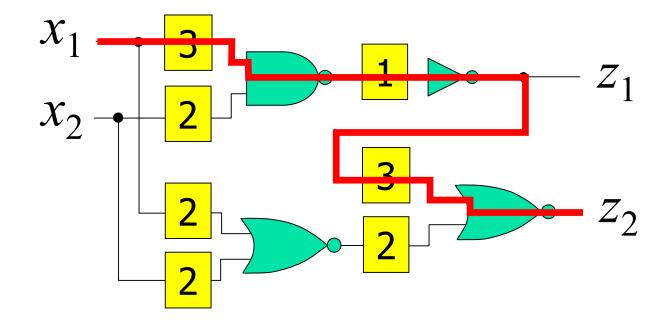

## クリティカルパス

#### 遅延が最大の経路

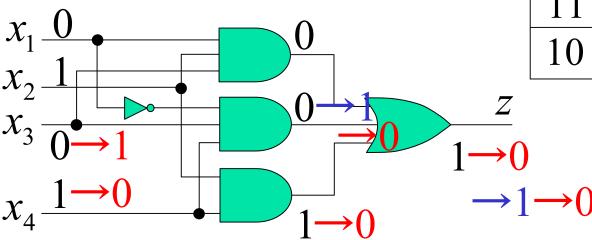

## ハザード

- 「ハザードが存在する」

- ■浮遊遅延のばらつき

- ■組合せ回路の出力に 瞬時的な不正パルス (可能性)

# ハザード

■静的ハザード 定常値同じ

$$0 \to 1 \to 0$$

0/1ザード  $1 \to 0 \to 1$  1/1ザード

動的ハザード 定常値異なる

$$0 \rightarrow 1 \rightarrow 0 \rightarrow 1$$

## 論理ハザード

## 回路構成に依存するハザード

$z = x_1 x_2 x_3 + \overline{x}_1 x_3 x_4 + x_2 \overline{x}_3 x_4$

| $x_1x_2$ | 00 | 01 | 11                  | 10 |

|----------|----|----|---------------------|----|

| 00       |    |    |                     |    |

| 01       |    | 1  | 1                   |    |

| 11       | 1  | 1  | $\boxed{1}$         |    |

| 10       |    |    | $\lfloor 1 \rfloor$ |    |

| 0                                         | 1 1                 | L |

|-------------------------------------------|---------------------|---|

| $x_1 = 0$                                 | 10                  |   |

| $x_2$ 1                                   |                     |   |

|                                           |                     |   |

| $X_3$ $0 \rightarrow 1$ $1 \rightarrow 0$ | $\longrightarrow 1$ |   |

| 1                                         | <i>J</i> 1          |   |

| $X_4 \xrightarrow{1} 0$                   |                     |   |

| 1 1                                       |                     |   |

1ハザード 存在

#### 全ての主項を含むAND-OR2段回路

$z = x_1 x_2 x_3 + \overline{x}_1 x_3 x_4 + x_2 x_4$

| 0                             | 11             |

|-------------------------------|----------------|

| $x_1 = 0$                     | 10             |

| $x_2$                         | $\overline{z}$ |

| $x_3 \xrightarrow{0 \to 1} 1$ |                |

| $\mathbf{r}$ 1                |                |

| $x_1x_2$ | 00 | 01 | 11 | 10 |

|----------|----|----|----|----|

| 00       |    |    |    |    |

| 01       |    | 1  | 1  |    |

| 11       | 1  | 1  | 1  |    |

| 10       |    |    | 1  |    |

Z

静的論理ハザード無

### 論理ハザード

#### 全ての主項を含むAND-OR2段回路

多入力変化

| $x_1x_2$ | 00 | 01                                          | 11 | 10 |

|----------|----|---------------------------------------------|----|----|

| 00       |    |                                             |    |    |

| 01       |    | 1                                           | 1  |    |

| 11       | 1  | $\left(\begin{array}{c}1\end{array}\right)$ | 1  |    |

| 10       |    |                                             | 1  |    |

動的論理ハザード有

### 関数ハザード

#### 全ての主項を含むAND-OR2段回路

多入力変化

| r = 0                                                                       | 11         |

|-----------------------------------------------------------------------------|------------|

| $\begin{array}{c} x_1 \\ x_2 \\ \hline \end{array}$                         | 10         |

| $X_2$ $X_3$ $0$ $1$ $0$ $1$ $0$ $1$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ | <b>→</b> 1 |

| $x_4 \xrightarrow{1} 0$                                                     | 1          |

| $x_1x_2$ | 00 | 01                                          | 11 | 10 |

|----------|----|---------------------------------------------|----|----|

| 00       |    |                                             |    |    |

| 01       | 1  | 1                                           | 1  |    |

| 11       |    | $\left(\begin{array}{c}1\end{array}\right)$ | 1  |    |

| 10       |    |                                             | 1  |    |

関数 ハザード有

## ハザード

- ■全ての主項を含むAND-OR 2段回路

- ■単一入力変化

- ハザード無し

- ■多入力変化

- ■動的ハザードの可能性

- 関数ハザード有り

## 論理回路の誤動作

- 過渡的な不正パルス

- ■組合せ回路

- 誤動作?

- ■同期式順序回路

- ■同時クロックパルス⇒誤状態遷移

- ■非同期式順序回路

- 誤動作

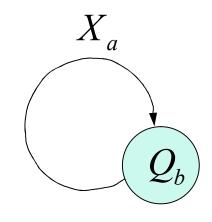

## 安定状態

$$\delta(X_a, Q_b) = Q_b$$

$Q_b$ :入力 $X_a$ の下での安定状態

状態遷移表⇒○で囲む

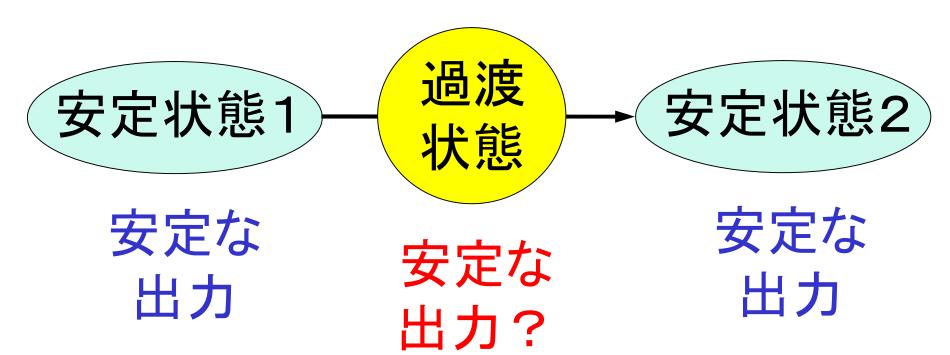

## 過渡状態

## 順序回路の誤動作防止

■非同期式順序回路

<方針>

入力変化の起点

安定状態

単一入力変化

→ 状態遷移先の確定