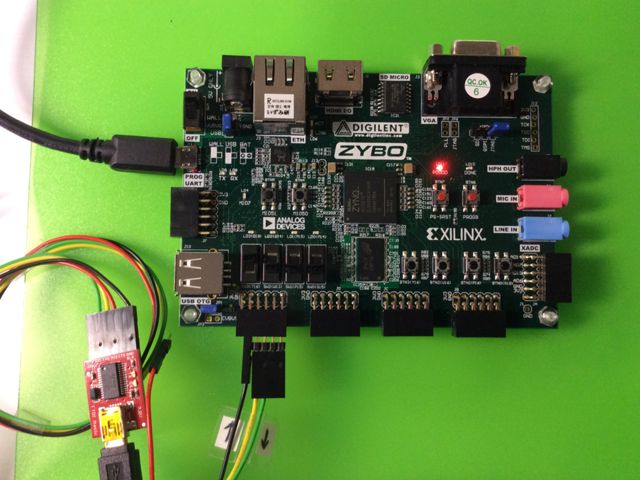

- ボードの JP5 が JTAG 側に刺さっていることを確認

- ボードの PROG UART に USB ケーブルを接続、電源投入、ドライバ類の認識を確認

- ボードをリセット (BTN7 PS-SRST)

- Flow Navigator 領域内、Program and Debug → Hardware Manager → Open Target → Open New Targetを実行、Local server から選択

- Flow Navigator 領域内、Program and Debug → Hardware Manager → Program Device → xc7z010

- LD10 DONE の点灯を確認

6. プロセッサシステム情報のエクスポート(Vivado)

ソフトウェア開発のためにプロセッサシステムの情報をエクスポートする。

- 上端メインメニューのFileから、Export → Export Hardware を実行。

- [ ] Include bitstream のチェックを外してOK。

7. ソフトウェア開発プロジェクトの設定(SDK)

Xilinx SDK 上でのソフトウェア開発環境をセットアップする。

7-1. SDK の起動

- Vivado の上端メインメニュー File から Launch SDK する。

- (SDKが起動できない→インストール確認)

- (次以降に SDK を立ち上げる時も Vivado のプロジェクトから Launch するのが無難)

7-2. プロジェクトの生成

- (A)上端メインメニュー File から New → Application Project

- Project name: testfifo に設定し、

(Finish ではなく) [Next] する。

- Hello World の Template を選択し、[Finish]する。

8. 動作確認 (Hello World) (SDK)

8-1. コンパイル

- (B) Project Explorer ウィンドウで testfifo 下 src 下 helloworld.c をダブルクリックして開く。

- (C)メインウィンドウでソースコードを確認する。必要なら編集して保存する。

- (A)上端メインメニュー Project から Build All する。

8-2. 標準入出力とUARTの接続

8-3. 実行と動作確認

- (B) Project Explorer で testfifo を右クリックし、

Run As → Launch on Hardware (System Debugger)を実行。

- (F)エリアの Terminalタブで、Hello Wolrd の出力を確認。

8-4. 再実行

- ボードをリセット (BTN7 PS-SRST)

- Vivado の Hardware Manager で Program Device

- SDK で Run As → Hardware

- Vivado の Hardware Manager で Reflesh Device

9. 動作確認 (psloopback) (SDK)

ここでは、PC から ZYNQ のプロセッサへデータを送り、そこで処理して PC に送り返す動作の確認を行う。

具体的にはターミナルエミュレータから文字を送り、大文字⇔小文字変換をして送り返す。

※SDK上のターミナルは使わない!

9-1. ソースコードの登録

- (B) Project Explorerのtestfifo/srcの下の helloworld.cを右クリックし、Delete

- Windows の Explorer から psloopback.c をドラッグし、SDK の Project Explorer ウィンドウ内のtestfifo/srcにドロップ、

(*)Copy files にチェックし、OK

9-2. コンパイル

- (A) 上端メインメニュー Project から Build All

9-3. SDK上のターミナルを切る

- (F)エリアのTerminalタブを選択

- Disconnect ボタンで接続を切る

9-3. ターミナルエミュレータの起動

9-4. 実行と動作確認

- ボードをリセット (BTN7 PS-SRST)

- Vivado の Hardware Manager で Program Device

- (B) Project Explorer で testfifo を右クリックし、Run As → Launch on Hardware (System Debugger)を実行。

- ターミナルエミュレータに文字を入力、大文字⇔小文字変換されて表示されることを確認

※SDK上のターミナルからは文字は送れないようだ。別途ターミナルエミュレータを開くこと。

10. コードの登録、コンパイル、実行

10-1. ソースコードの登録

- (B) Project Explorerのtestfifo/srcの下の psloopback.cを右クリックし、Delete

- Windows の Explorer から testfifo.c をドラッグし、SDK の Project Explorer ウィンドウ内のtestfifo/srcにドロップ、

(*)Copy files にチェックし、OK

10-2. コンパイル(SDK)

- (A) 上端メインメニュー Project から Build All

10-3. UARTの追加

この動作テストでは、追加のUARTを必要とする。

- USB-UART モジュールと配線材を用意

(sparkfun FTDI Basic, aitendo USB2UART-CP2102 等)

- PCへのドライバのインストール、PCとの接続

- コンピュータ→プロパティ→デバイスマネージャで COM ポート番号を確認しておく

- ZYBO Pmod JE ポートに接続

| USB-UART モジュールのピン | ZYBO Pmod JE のピン | FPGA内での接続 |

|---|

| モジュールからのデータ出力 | JE3(上段右から3番目) | UART TX (FPGAからの出力) |

| モジュールへのデータ入力 | JE4(上段右から4番目) | UART RX (FPGAへの入力) |

| GND | GND(上下段左から2番目) | - |

※PC側から見た送信データ(TX/出力)はFPGA側から見れば受信データ(RX/入力)である。信号名はどちら側の観点から名付けるか、で変わる。

信号名だけではなく入出力の方向を確認すること!

※接続を間違えるとボードが壊れる。

ZYBO FPGA Board Reference Manual の p.24 の「16 Pmod Connectors」と、

USB-UART モジュールの資料をよく読んで確認すること。

わからなければ、詳しい先輩や教員に尋ねること。

10-4. ターミナルエミュレータの起動

10-5. 実行

- ボードをリセット (BTN7 PS-SRST)

- Vivado の Hardware Manager で Program Device

- (B) Project Explorer で testfifo を右クリックし、Run As → Launch on Hardware (System Debugger)を実行。

11. 動作確認(SDK,Vivado)

11-0. 信号観測の準備

- SDK で Run As → Launch on Hardware した後に

Vivado Hardware Manager で Reflesh Device (必要なら(1)の辺りに出る)すると

実機デバッグが可能になる。

- ILA の Setting (2)

- Capture Mode: BASIC

- Trigger position in window: 32

- Trigger Setup (3)

- + (Add Probes)を押して arm_m0valid を追加

- Compare Value の Value を R (0->1) にする

- 同様に arm_m1valid, arm_s0valid, arm_s1valid を追加し R に設定

- ゲート記号マークを押してトリガ条件を論理和に設定(Set Trigger Condition to Global OR)

- Status (4) で観測開始(右向き三角に縦棒)

- AXI Data Stream の出入があると、その波形が表示される

- 表示を拡大縮小、移動して確認(5)

11-1. 直接接続 M0, S0 ポートの動作テスト(SDK)

- ボードの SW3,SW2,SW1,SW0 を0000にしておく

- ボードのBTN0を押すとM0にデータを送り出す

- ボードのBTN2を押すとS0からデータを受け取る

- ポートのビジー状態、送受データなどが SDK の Terminal に表示される

- M0 のビジーが0の時に送り出したデータの下位4bitが

ボードのLD3,LD2,LD1,LD0に表示される

- S0 のビジーが0の時に読み出すと「LEDの値+SWの値」の値が読み出される

- M0 のビジーが1の時に送り出したデータは無視される

- S0 のビジーが1の時に読み出したデータは不正(直前の値のまま)

- BTN0, BTN2 を様々な順番で押してみて、上記の動作を確認

発展:zybo_top.v の AXIS_LB_THROUGH を 1 にして

ハードウェアをコンパイルしなおすと、

valid, ready を無視したレジスタ型の動作を確認できる。

11-2. M1 ポートの1文字書き出し動作テスト

- ボードの SW3,SW2,SW1,SW0 を0000にしておく

- ボードのBTN1を押すとM1にデータを送り出し、UARTを経由してPCのターミナルエミュレータに表示される

- SDK の Terminal に表示される送信状況と、ターミナルエミュレータに表示される受信内容を見比べて、動作を確認する。

※人がボタンを押す速度は UART に比べて充分に遅いので、ここでは M1 Busy で待たされることはない

11-3. M1 ポートの複数文字書き出し動作テスト

- ボードの SW3,SW2,SW1,SW0 を1000にしておく

- ボードのBTN1を押すとM1にデータを送り出し、UARTを経由してPCのターミナルエミュレータに表示される

- Write Port 1 のFIFOの残容量を確認し、書込可能な文字数を連続して送る。

- SDK の Terminal に表示される送信状況と、ターミナルエミュレータに表示される受信内容を見比べて、動作を確認する。

※SWを1111にすると、FIFOの残容量以上のデータを連続して送る。UARTの速度はプロセッサの書き込み速度に比べてとても遅いので、書き込めなかったデータは無視され、捨てられる。なお、M1から出た先のレジスタやFIFOのため、FIFO残容量以上のデータが書きこまれることもあるが、それは保証されない。

11-4. S1 ポートの1文字読み込み動作テスト

- ボードの SW3,SW2,SW1,SW0 を0000にしておく

- ボードのBTN3を押すと、PCのターミナルエミュレータに入力された文字が

UARTを経由してS1からデータを受け取る。

- ターミナルエミュレータから入力した文字と

SDK の Terminal に表示される受信状況を見比べて、動作を確認する。

※人がボタンを押す速度は UART に比べて充分に遅いので、ここでは M1 Busy で待たされることはない

11-5. S1 ポートの複数文字読み込み動作テスト

- ボードの SW3,SW2,SW1,SW0 を1000にしておく

- ボードのBTN3を押すと、PCのターミナルエミュレータに入力された文字が

UARTを経由してS1からデータを受け取る。

- Read Port 1 のFIFOのデータ量を確認し、読出可能な文字数を連続して読む。

- ターミナルエミュレータから入力した文字と

SDK の Terminal に表示される受信状況を見比べて、動作を確認する。

※SWを1111にすると、FIFO内のデータ数以上を連続して読む。UARTの速度はプロセッサの書き込み速度に比べてとても遅いので、読み出せなかったデータは不正なものとなる。なお、S1以前のレジスタやFIFOのため、FIFO内のデータ数以上のデータが読めることもあるが、それは保証されない。

99. その他

Verilog デバグ〜埋もれたタイプミスを見つける

Verilog では、信号を宣言せずに使用してもよい。

なので、タイプミスをしてもエラーにならない。

そのようなバグを見つけるためには、

Messages から次の Warning を検索して確認するとよい。

- [Synth 8-3331] unconnected port

- [Synth 8-3848] does not have driver

- [Synth 8-3295] tying undriven pin to constant

Zynq の実機での実行について

何故かうまくいかない。経験的に成功率の高い方法は…

- プロセッサをリセット(PS-RST,PS-SRSTのボタン)する

- Program FPGA する

- Run As, Hardware する

その他の対処として…

- Terminal をいったん Disconnect して Connect しなおしてみる

- ボードの電源をいったん切って、再投入してみる

Zynq の実機デバッグ時の実行

PL側に回路をコンフィグしただけではデバッグモジュール(ILA)が認識されないようだ。

PS側でソフトウェアを実行すると認識される。

経験的に成功率の高い方法は…

- ボードでプロセッサをリセット(PS-RST,PS-SRSTのボタン)する

- Vivado の Hardware Manager で Program Device する

- SDK で Run As, Hardware する

- Vivado の Hardware Manager で Reflesh Device する

Zynq の COMポートが認識できない

いちど削除して、ドライバをインストールしなおすと認識することがあるかもしれなくもない…。

- ボードをPCから外す

- PCの電源を切る

- PCを起動する

- 後述の方法で未使用COMポートを削除

- PCの電源を切る

- ボードを接続する

- PCを起動する

- 認識するかどうか確認(しばらく時間がかかる)→認識すればそれでOK

- Windows のデバイスマネージャーから、表示→デバイス(種類別)して当該デバイスを探す。

Cypress の USB Serial というような表示になると思われる。

- デバイスドライバを再インストールする。