# 同期FIFOのFPGAベンダ非依存 記述と高速化設計

立命館大学 理工学部 電子情報工学科 大学院 理工学研究科 電子システム専攻 泉 知論

#### FPGAベンダと設計環境

- 各社競い合ってよりよい設計環境、ライブラリを提供。

- 一方で、ユーザはベンダ依存の設計を強いられる。

AでもXでもどちらでも使いまわせる設計をしたい (少なくとも、情報処理のコア部分、汎用部品、基本部品は)

# 脱ベンダ依存計画

XIIIX

非依存

ALTERA

高位合成ツール

VIVADO HLS

サードパーティーのツール Impulse

C2H

MICRO BLAZE 公的検定試験用プロセッサ COMET II

ソフトコアプロセッサ

NIOS II

基本ライブラリ

CORE GENERATOR

ベンダ非依存記述

MEGA WIZARD

### ほぼ同じ v.s. 全く同じ

- FIFO は基本部品

- Altera も Xilinx も IP を提供

- 機能、入出力はほぼ同じ

- 仕様の確認、互換性の確認

- 必要なら極性、論理、タイミングの微修正

- 書き換えても1行~数行

- ライブラリ生成ツール、パラメタ設定、生成、登録

- 誰が互換性を保証するか

V.S.

- ファイルをコピーするだけ

- 何も考えない、何も作業しない、何も心配しない

#### FIFOとデバイスへの依存性

- ストリーミング処理、データ駆動処理に必須

- 小さなFIFOはレジスタで実装可能→デバイス 非依存コードが容易にできる

- 大きなFIFOはメモリで実装→若干複雑な動作→通常はIP利用→デバイス依存

- 単純なRAMモデルは比較的移植性が高い

- デバイス非依存な RTL コードを開発 ※ここでは Verilog HDL を使用

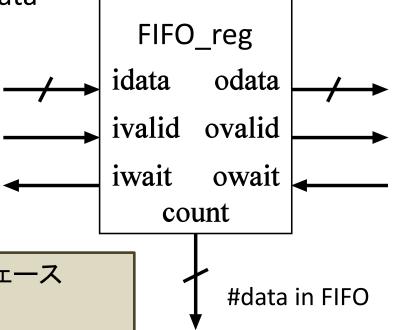

### (1) register 高速 FIFO

• レジスタで実装、小容量で高速

- スループット: 1 cycle per 1 data

- レイテンシ:1 cycle

どこでも通る記述

補足:いずみ研的ストリームインターフェース

- データ線+制御線

- 送信側の valid, 受信側の wait

- 転送成立 iff (valid==1)&&(wait==0)

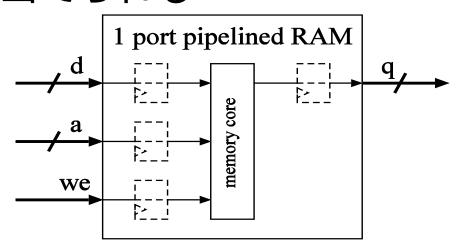

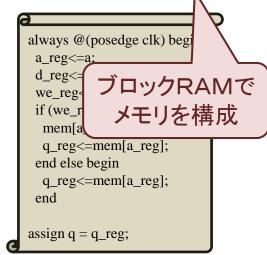

#### 基本部品:汎用 block RAM

- 1 port pipelined read/write

- 0, 1, or 2 cycles delay

- 「よくある」仕様

- 平易な記述で BRAM に割り 当てられる

description for 2cycles delay

```

always @(posedge clk) begin

a_reg<=a;

d reg<=d;

we_reg<=we;

if (we_reg) begin

mem[a_reg]<=d_reg;

q_reg<=mem[a_reg];

end else begin

q_reg<=mem[a_reg];

end

assign q = q_reg;

```

#### 汎用メモリ記述と使用リソース

|                                 | no delay         |                      | 1cycle delay     |                      | 2cycles delay    |                      |

|---------------------------------|------------------|----------------------|------------------|----------------------|------------------|----------------------|

| Xilinx<br>XC5VLX30<br>ISE 14.4  | Logic<br>(Slice) | Memory<br>(36k BRAM) | Logic<br>(Slice) | Memory<br>(36k BRAM) | Logic<br>(Slice) | Memory<br>(36k BRAM) |

|                                 | 172              | 0                    | 10               | 1                    | 10               | 1                    |

| Altera EP4CE115 Quartus II 12.0 | Logic<br>(LE)    | Memory<br>(bit)      | Logic<br>(LE)    | Memory<br>(bit)      | Logic<br>(LE)    | Memory<br>(bit)      |

|                                 | 46043            | 0                    | 99               | 32768                | 65               | 32768                |

ロジックリソースで メモリを構成 always @(posedge clk)

if (we) mem[a]<=d;

assign q = mem[a];

8bit × 4096 words メモリ+αを合成した結果 always @(posedge clk) begin

a\_reg<=a;

d\_reg<=d;

we\_reg<=we;

if (we\_reg)

mem[a\_reg]<=d\_reg;

assign q = mem[a\_reg];</pre>

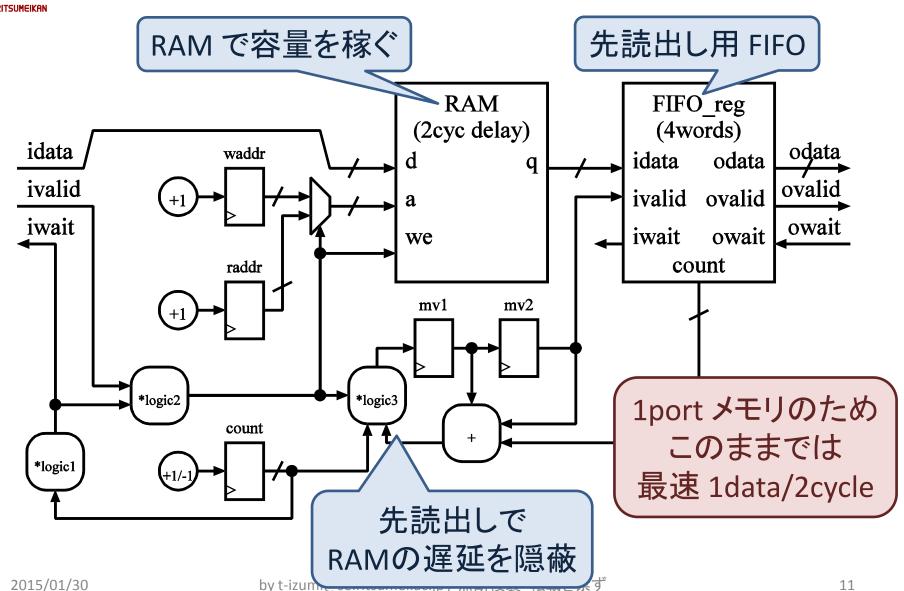

### (2) block RAM低速FIFO

- 2 cycles delay の pipelined single port memory を使用

- メモリ読出しのレイテンシを先読み出しバッファで隠蔽

- 相対的に大容量で低速

- スループット: 2 cycles per 1 data

- レイテンシ: 4 cycles

- ベンダ非依存記述

#### 2t FIFO

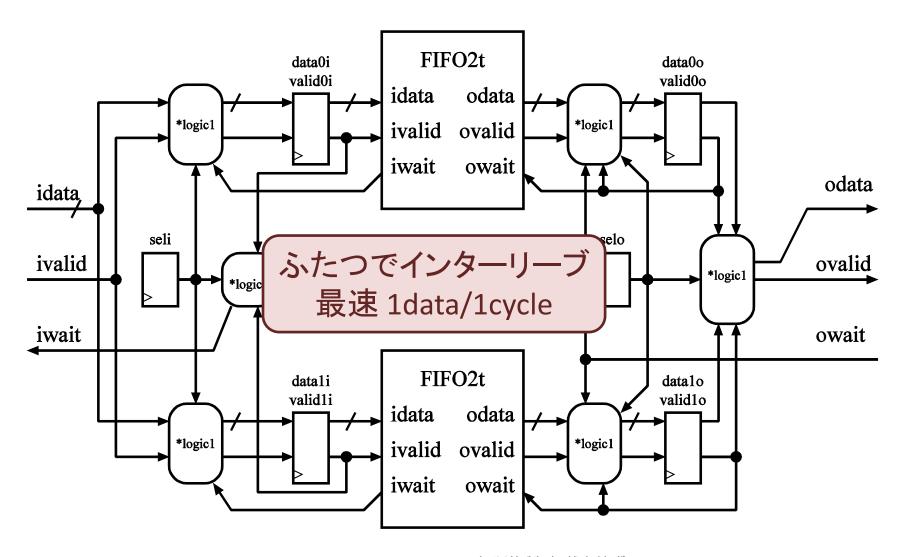

#### (3) block RAM高速FIFO

- 2t FIFO ふたつでインターリーブする

- 相対的に大容量で高速

- スループット: 1 cycle per 1 data

- レイテンシ: 6 cycles

- ベンダ非依存記述

## インターリーブ FIFO

#### 合成&実装

| XILINX       |                    |  |  |  |

|--------------|--------------------|--|--|--|

|              | T-1CSG324C<br>14.4 |  |  |  |

| IP Generator | 非依存記               |  |  |  |

| <b>42</b>    | 75.                |  |  |  |

IP Generator非依存記述43 slices\*75 slices\*2 RAMB36s\*2 RAMB36s\*

126 MHz

記述 ロジック量 メモリ量

最大クロック

| ALTERA                           |             |  |  |  |

|----------------------------------|-------------|--|--|--|

| EP4CE115F29C7<br>Quartus II 12.0 |             |  |  |  |

| 非依存記述                            | Mega Core   |  |  |  |

| 272 LEs*                         | 78 LEs*     |  |  |  |

| 65536 bits*                      | 65536 bits* |  |  |  |

| 62 мнг                           | 289 мнг     |  |  |  |

- 8bit×8192words のFIFOを実装

- リソース量\*は全体の合成結果から周辺のみの合成結果を引いた値

- IP Generator, Mega Core の機能/インターフェースをほぼ同じにした (common clock, read timing, data count, sync reset)

(throughput, latency は未確認)

235 мнг

#### まとめ

- 同期FIFOのFPGAベンダ非依存なライブラリ化設計

- register 1cycle/data FIFO

- bRAM 2cycle/data FIFO

- bRAM 1cycle/data FIFO

- 十分に小さく、速い

- チューンの余地あり

- 2port RAM の検討

- Verilog HDL 記述、ビット幅、容量パラメタ設定可能

- 公開しています

www.ritsumei.ac.jp/se/re/izumilab/dist/fifo4any.htm