(C) by T.IZUMI, Aug 2015

Ver. 2015.09.28b

組込みシステム開発トレーニング課題

Xilinx Vivado による MicroBlaze と周辺回路、ソフトウェアの開発サンプル

ソースコードを含むアーカイブ一式はこちら:

http://www.ritsumei.ac.jp/se/re/izumilab/lecture/15Nexys4MbVivado.zip

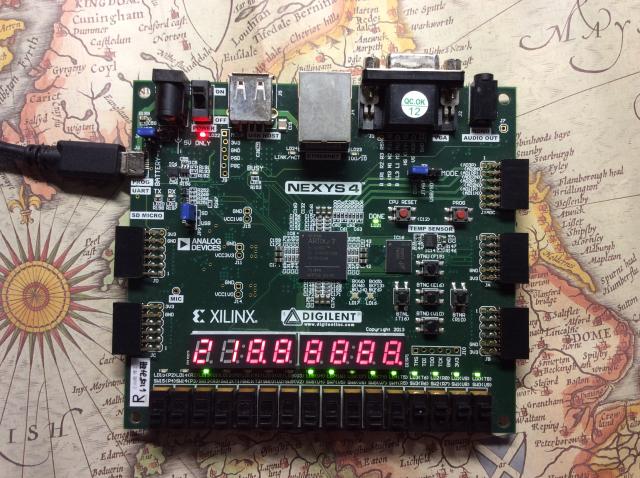

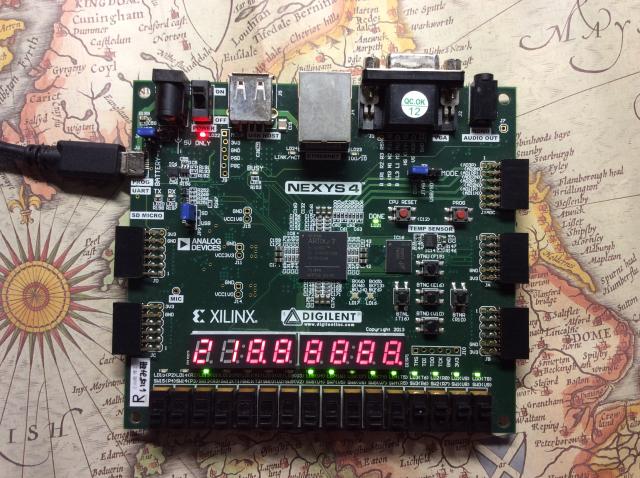

- ターゲットボード

- Nexys-4

- ターゲットFPGA

- XC7A100T-1CSG324C

- (他のボードでトライする場合は、ボードの仕様に合わせてxdcファイルとトップ記述を書き換える)

- 開発環境

- Xilinx Vivado 2015.2

- Xilinx SDK 2015.2

- ※SDK のインストール確認

- Helpにある「Add Design Tools or Devices 2015.2」にてSDKがダウンロードされているか確認

- ※SDK の追加インストール

- Xilinxのホームページでエラーコードを検索

(AR#55559)

- Helpにある「Add Design Tools or Devices 2015.2」から「Software Development kit」を選択し追加する。

- SDK をインストールしたら、コマンドプロンプトにて

C:\Xilinx\Vivado\2015.2\settings64.batを実行

C:\Xilinx\SDK\2015.2\settings64.batを実行

C:\Xilinx\Vivado\2015.2\bin\Vivado.batを実行

(実行前にプロジェクトは閉じておく)

- この課題の習得項目は次の通り。

- Vivado IP Integrator による Micro Blaze システムの構築

- Xilinx SDK によるソフトウェア開発

- Nexys-4 による実機動作確認

- この課題は次の項目を習得済みの者を対象とする。

- 計算機アーキテクチャの基本(プロセッサ、バス、メモリ、レジスタ、I/O)

- Verilog 記述、シミュレーション

- Vivado 基本操作(→Nexys-4による回路設計演習Vivado版推奨)

- LED/SW の取扱い

- UART の取扱い

- C言語

- OS, コンパイラの基本

- この課題終了後には次の課題を推奨する。

- 以下、特に指定の無い項目は規定値(デフォルト、最初から入っている値)を設定する。

- Vivado は深くフォルダを掘ってトラブルを起こすので、

課題を実行するフォルダにドライブ文字を割り当てておくとよい。

subst_dir.bat のフォルダ名を変更して実行すると良い。

1. プロジェクトの生成(Vivado)

- Vivado を起動する。

既存のプロジェクトが開いていたら [File] -> [Close Project] する。

1-1. プロジェクト生成

1-2. 画面の確認

- 左側 Flow Navigator (A)で、大まかに何をするか指定する。

- 右側 (B)で、各種設定、操作指示、ファイル編集、などを行う。

- 下側 (C)で、ログや状況の確認を行う。

- 見たい画面が行方不明なときのチェックリスト

- それぞれの領域のタブ(矢印の先)で切り替える

- (A)Flow Navigator で対象手順を選択

- (B1)対象のファイル、モジュール、信号などを選択

- (B2)で対象のオブジェクトを選択

- 上端メインメニューの Window(赤矢印)で選択

1-3. ソースファイルの登録

- 上端メインメニュー File, Add Sources を選択。

- (*) Add or create constraints を選択。

- +を押下、Add Files を実行、Nexys4.xdc を登録。

- 同様に、上端メインメニュー File, Add Sources を選択。

- (*) Add or create design sources を選択。

- +を押下、Add Files を実行、Nexys4_top.v, hexilum.v, random32.v を登録。

- (B1)ウィンドウで Sources タブを選ぶ。

- Design Sources の中に登録したモジュールがあることを確認する。

- Nexys4_top がトップ(太字)になっていることを確認する。

もしも Nexys4_tb がトップになっていたら、

Nexys4_topを右クリックして Set as Top する。

- Constraints の中に Nexys4.xdc があることを確認する。

- それぞれのモジュールやファイルをダブルクリックすると

(B2)ウィンドウにファイルが表示されることを確認する。

そこで編集や保存もできる。

2. システム構築(Vivado)

2-1. Block Design の登録

- (A) Flow Navigator の IP Integrator から Create Block Design を実行。

- Design name = mb として生成。

- 右側にBlock Design のウィンドウ群が現れる。

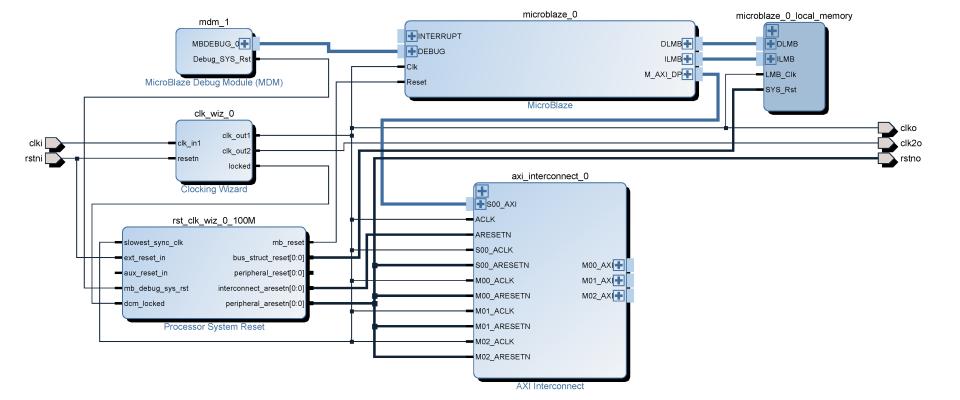

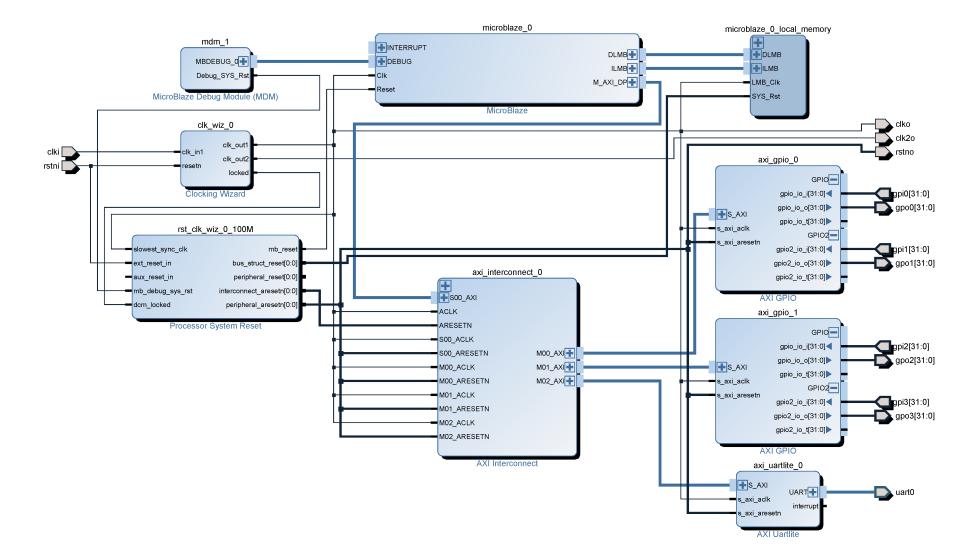

2-2. MicroBlaze と基本モジュールの配置

- Diagram ウィンドウ(B2)の左側+ボタンを押下してMicroBlazeを追加。

- Diagram ウィンドウ内の下地で右クリック、Run Block Automation を実行。

- Local Memory: 32KB、Peripheral AXI Port: Enabled に設定。

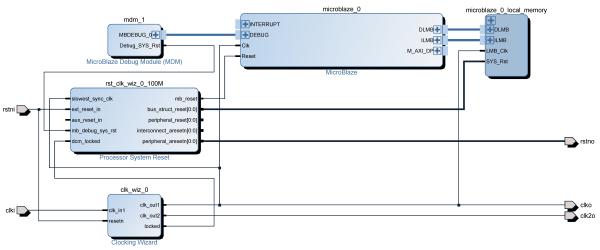

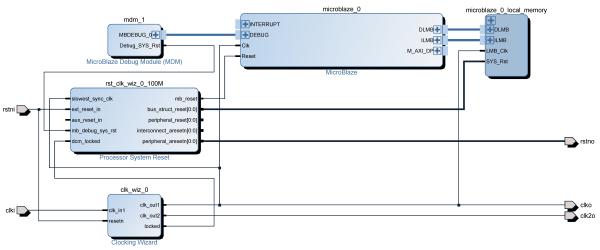

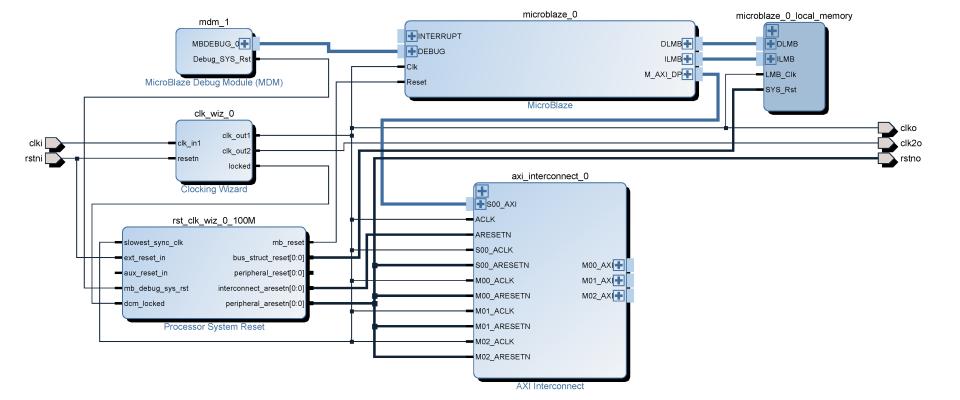

- Diagram ウィンドウ内に Clocking Wizard, MicroBlaze Debug Module(MDM), Processor System Reset, local memory が配置され接続されていることを確認。

- Diagram ウィンドウ内で MicroBlaze を右クリックし Customize Block

- Page 1, [*] Select implementation to optimize area をチェック

- Page 4, [*] Enable Peripheral AXI Data Interface をチェック

- Diagram ウィンドウ内で Clocking Wizard を右クリックし Customize Block

- [Clocking Options]タブ、Input Clock Information, Primary の Imput Frequency を Manual にして 100MHz, Source を Single ended clock capable pin に設定。

- [Output Clocks]タブ、[*]clk_out2をチェック、Output Freq=50MHzに設定。

- [Output Clocks]タブ、Reset Type、(*) Active Low にチェック。

- リセット、クロックの外部接続

- クロック入力

- Diagram ウインドウ内の下地で右クリック、Create Portする。

- Port name: clki, Direction: Input, Type: Clock, Frequency: 100

- Diagram ウインドウ内で clki ポートにマウスカーソルをあて、鉛筆カーソルになったところでドラッグし Clocking Wizard の clk_in1 に接続する。

- clki ポートにマウスカーソルをあて、指カーソルになったところでダブルクリックし、Freq Hz が100000000であることを確認する。

- クロック出力(100MHz)

- Port name: clko, Direction: Output, Type: Clock

- Clocking Wizard の clk_out1 に接続

- クロック出力(50MHz)

- Port name: clk2o, Direction: Output, Type: Clock

- Clocking Wizard の clk_out2 に接続

- 指カーソルでダブルクリックし、Freq Hz を50000000に設定。(単位がMHzではなくHzであることに注意)

- リセット入力

- Port name: rstni, Direction: Input, Type: Reset, Polarity: (*) Active Low

- Clocking Wizard の resetn に接続, さらに Processor System Reset の ext_reset_in に接続

- 指カーソルでダブルクリックし、Polarity が Active Low であることを確認する。

- リセット出力

- Port name: rstno, Direction: Output, Type: Reset

- Processor System Reset の peripheral_aresetn に接続

- 指カーソルでダブルクリックし、Polarity が Active Low であることを確認する。

- ブロック図の整理…指マーク状態で移動、左側の再配置ボタンなどを使用して、図を整理しておくと良い。

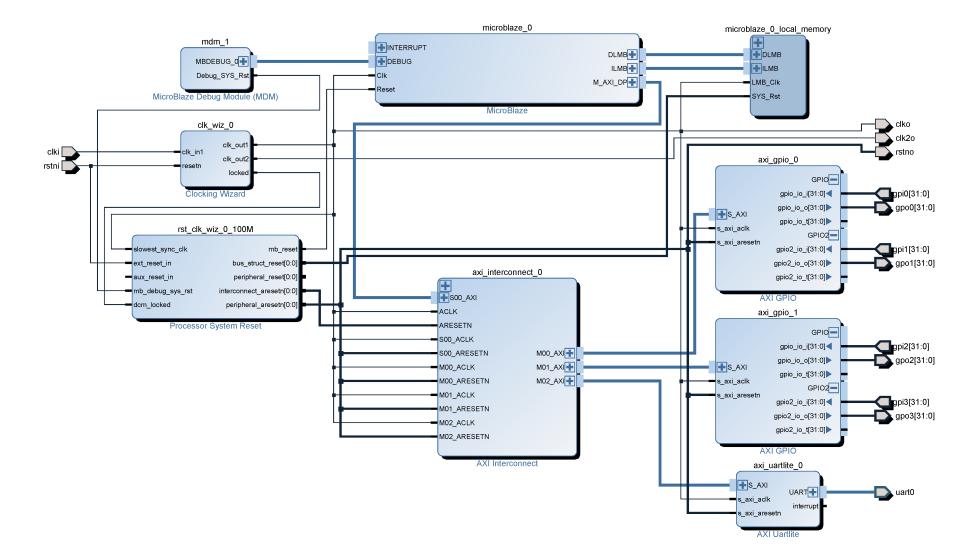

2-3. 周辺回路インターフェースの追加

- Diagram 下地を右クリック、Add IP で AXI Interconnect を追加。

- AXI Interconnect を右クリック、Customize Block する。

- [Top Level Settings]タブ、Number of Master Interfaces = 3 にする。

- 鉛筆カーソルで以下を接続する。

- S00_AXI → MicroBlaze の M_AXI_DP

- ACLK, ○○_ACLK すべて → Clocking Wizard の clk_out1

- ARESETN → Processor System Reset の interconnect_aresetn

- その他の○○_ARESETN すべて → Processor System Reset の peripheral_aresetn

2-4. GPIO の追加

32bit の入力を4つ、出力を4つ作成する。

- Add IP で AXI GPIO をふたつ追加

- 右クリック Customize Block で [*] Enable Dual Channel にチェック(両方)

- axi_gpio_0 の S_AXI を AXI Interconnect の M00_AXI に接続

- axi_gpio_1 の S_AXI を AXI Interconnect の M01_AXI に接続

- 両方の s_axi_aclk を Clocking Wizard の clk_out1 に接続

- 両方の s_axi_aresetn を Processor System Reset の peripheral_aresetn に接続

- axi_gpio_0 モジュールの GPIO インターフェースの+をクリックして展開

- gpio_io_i[31:0] を右クリック、Make External する。

- 出来た外部ポートを指カーソルで選択し、External Port Properties

- 左側 External Port Properties 画面(B3)で Name: gpi0 に設定

- 以下同様に、インターフェースの展開、外部ポート作成と名前設定を行う

- axi_gpio_0 の gpio_io_i → gpi0

- axi_gpio_0 の gpio_io_o → gpo0

- axi_gpio_0 の gpio2_io_i → gpi1

- axi_gpio_0 の gpio2_io_o → gpo1

- axi_gpio_1 の gpio_io_i → gpi2

- axi_gpio_1 の gpio_io_o → gpo2

- axi_gpio_1 の gpio2_io_i → gpi3

- axi_gpio_1 の gpio2_io_o → gpo3

2-5. UART の追加

- Add IP で AXI Uartlite を追加

- 右クリック Customize Block で Baud Rate=115200, Data Bits=8, No Parity に設定する。

- S_AXI を AXI Interconnect の M02_AXI に接続

- s_axi_aclk を Clocking Wizard の clk_out1 に接続

- s_axi_aresetn を Processor System Reset の peripheral_aresetn に接続

- UARTインターフェースを(展開しないで)右クリック、Make External する。

- 出来た外部ポートを指カーソルで選択し、External Port Properties

- 左側 External Port Properties 画面で Name: uart0 に設定

2-6. アドレス空間の設定

- ウィンドウ(B2)上部 [Address Editor] タブを開く。

- それぞれの項目を展開して割り当てられているアドレスを確認する。

- Unmapped Slaves があれば右クリックし Auto Assign Address する。

2-7. システム生成

- ウィンドウ(B2)上部 [Diagram] タブを開く。

- Diagram 下地で右クリック、Validate Design

- 何か問題があったら警告が出るので対処する

- Flow Navigator(A) の IP Integratorメニュー内 Generate Block Design を実行

- Flow Navigator(A) の Project Manager を選択

- Souces ウィンドウ(B1)内、Design Sources の mb(mb.bd) を右クリックし Create HDL Wrapper を実行する。

- Sources ウィンドウ内、Design Sources の中に mb_wrapper(mb_wrapper.v)があるのを確認する。

- mb_wrapper をダブルクリックし、モジュールの入出力を確認する。

3. コンパイル(Vivado)

- Flow Navigator領域内、Synthesis の Run Syntehsis を選択、実行。

- Flow Navigator領域内、Implementation の Run Implementation を選択、実行。

- Flow Navigator領域内、Program and Debug の Generate Bitstream を選択、実行。

- 各段階でProject Navigator 領域の右上 Project Summary, 下 Messages, Log, Reports などを確認。

- 必要に応じて、ファイルを編集し再実行。Flow Navigator 領域内左上 Sources でソースファイルを選択し開いて、左上で編集・保存する。

4. プロセッサシステム情報のエクスポート(Vivado)

ソフトウェア開発のためにプロセッサシステムの情報をエクスポートする。

- 上端メインメニューのFileから、Export → Export Hardware を実行。

- ハードウェアを確定してあとはソフトウェアの開発・実行・修正の繰り返しであれば、ここで [*] Include bitstream しておく。

5. ソフトウェア開発プロジェクトの設定(SDK)

Xilinx SDK 上でのソフトウェア開発環境をセットアップする。

SDK の起動

- Vivado の上端メインメニュー File から Launch SDK する。

- (SDKが起動できない→インストール確認)

- (次以降に SDK を立ち上げる時も Vivado のプロジェクトから Launch するのが無難)

プロジェクトの生成

- 上端メインメニュー File から New → Application Project

- Project name: peripherals_test に設定し、[Finish]

- Project Explorer ウィンドウ(A)内の peripherals_testを右クリックし、Generate linker scriptを実行。そのままOK、lscript.ld を overwriteする。

- Project Explorer ウィンドウ内の peripherals_test を展開し、src を展開する。

- なぜか自動生成されている gpio_header.h, testperiph.c, xgpio_tapp_example.c を削除(右クリック→Delete)

- Windows の Explorer から peripherals_test.c をドラッグし、SDK の Project Explorer ウィンドウ内のperipherals_testの下のsrcにドロップする。

- (*)Link to files にチェックする。(コピーしたければ Copy files)

6. ソフトウェア開発とコンパイル(SDK)

- Project Explorer ウィンドウで peripherals_test 下 src 下 peripherals_test.c をダブルクリックして開く。

- メインウィンドウでソースコードを確認する。必要なら編集して保存する。

- 上端メインメニュー Project から Build All する。

- Project Explorer ウィンドウで peripherals_test の下 Debug の下に

実行型式peripherals_test.elfが生成されていることを確認。

- (Vivadoで Include bitstream して export していれば、ここで Xilinx Tools → Program FPGA でき、デバッガも使える)

7. ソフトウェアの登録(Vivado)

- 上端メインメニュー File, Add Sources を選択。

- (*) Add or create design sources を選択。

- +を押下、Add Files を実行。

- nexys4mb\nexys4mb.sdk\peripherals_test\Debug の peripherals_test.elf を登録。

- 同様に (*) Add or create simulation sources で peripherals_test.elf を登録。

- 上端メインメニュー Tools からAssociate ELF Files を実行。

- Design Sources \ mb/mb_i \ microblaze_0 に peripherals_test.elf を選択。

- Simulation Sources \ sim_1 \ mb/mb_i \ microblaze_0 も peripherals_test.elf を選択。

8. コンパイル(ソフトウェアを含む)(Vivado)

- Flow Navigator領域内、Program and Debug の Generate Bitstream を選択、実行。

9. ボードのコンフィグ(Vivado)

以下 a, b, c のいずれかの方法でコンフィグする。

9a. 直接コンフィグレーション

- FPGA を直接コンフィグレーションする。手軽で速いが電源を切ると消える。

- Flow Navigator領域内、Program and Debug の Hardware Manager の Open Target を選択、localhost???が登録済みなら選択。(無ければOpen New Targetを実行、Local server から選択)

- 右画面、右上の localhost の中の xc7a100t_0 を右クリックし Program Device を実行する。

9b. USB メモリに書き込む

- USB メモリに書き込み起動。ケーブル不要、電源投入で自動コンフィグ。

- PC で bit ファイルを USB メモリに書き込む。トップにひとつだけ書き込むこと。

- USBメモリをボードに挿し、PROGボタン押下あるいはボード再起動。

9c. オンボード FLASH ROM に書き込む。

オンボードオンボード FLASH ROM に書き込む。手間と時間はかかるが、電源投入に自動コンフィグ。

bin file を生成する方法

mcs file を生成する方法

- xdc ファイルに次を記述する。

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

set_property CONFIG_MODE SPIx4 [current_design]

- 下部画面 Tcl Console で以下のコマンドを実行する。(注 -size は MBytes で指定するので 128Mbit -> -size 16)

# write_cfgmem -format mcs -interface SPIx4 -size 16 -loadbit "up 0x0 ./nexys4mb.runs/impl_1/Nexys4_top.bit" -file Nexys4_top.mcs

- Hardware Manager で Mempry Part は s25fl128sxxxxxx0-spi-x1_x2_x4 を指定して書き込む。または Tcl Console で以下のコマンドを実行する。

# program_flash -f Nexys4_top.mcs -flash_type s25fl128sxxxxxx0-spi-x1_x2_x4 -verify -cable type xilinx_tcf url tcp:localhost:3121

10. 実機実行と動作確認

10.1. MicroBlazeを含まない動作の確認

- (リセットやクロックなどより基本的な部分の動作確認のため)

- Nexys4_top.v: LEDs の部分参照。

- 16bit Slide SW下位8bitを0にする→ 16bit LED が全消灯

- 1,2,3...8(二進数)にする→ 16bit LED が右から1,2,3...8個点灯。

- 9にする→ 16bit LED がカウントアップ

10.2. MicroBlazeによるGPIO動作の確認

- Nexys4_top.v: testcircuits の部分、7seg LEDs の部分参照。

- gpio0 の入力にはボタンとスライドスイッチが接続されている。

- gpio1 の入力にはカウンタ値が接続されている。

- gpio2 の入力には乱数値(CRC32)が接続されている。

- gpio3 の入力には乱数値(CRC32)が接続されている。

- Slide SW下位8bitを0にする→ gpio0 の出力を 7seg LED に表示

- Slide SW下位8bitを1にする→ gpio1 の出力を 7seg LED に表示

- Slide SW下位8bitを2にする→ gpio2 の出力を 7seg LED に表示

- Slide SW下位8bitを3にする→ gpio3 の出力を 7seg LED に表示

- peripherals_test.c の gpio 関連記述参照。

- SW下位8bitを0にする → 7seg がカウントアップし、BTNCを押すとカウントダウンする。

- SW下位8bitを1にする → UART(後述)で受け取った文字数の表示。

- SW下位8bitを2にする → ボタンとスライドスイッチの値を表示する。

- SW下位8bitを3にする → while(1) 周期実行にかかるクロックサイクル数の表示

10.3. MicroBlazeによるUART通信の確認

- PC と Nexys-4 を接続する。

- PC で Teraterm 等の端末エミュレータを立ち上げ、シリアル接続する。設定は 115200bps, 8bit, no parity, 1 stop bit, no flow control

-

- Nexys-4ボード上の十字ボタン(BTNC,BTNL,BTNR,BTNU,BTND)やスライドスイッチを操作すると、その値がPC側の端末エミュレータに8桁16進数で表示される。

- PC から文字を送ると、大文字⇔小文字変換されて帰ってくる。

- ボードのSW下位8bit を1にして、PCから文字を送ると7seg LEDに送った文字数(16進数)が表示される。

99. その他

Windows の COM ポート番号について

Windows は接続したことのあるデバイスを覚えていて、

COM ポート番号を使いまわす。

そのため、新しいデバイスを接続するたびにポート番号が増えていく。

ツールによっては COM ポートの番号が一桁でなければ正常動作しないものがある。

番号を振り直すには、不使用ポートを削除して接続し直す。

- コンピュータのプロパティから詳細設定、環境変数の設定で DEVMGR_SHOW_NONPRESENT_DEVICES を 1 に設定する。

- デバイスマネージャを起動、表示→非表示のデバイスを表示

不要なポートを削除。