(C) by T.IZUMI, Aug 2015

Ver. 2015.10.19a

組込みシステム開発トレーニング課題

Xilinx Vivado による回路開発のサンプル

ソースコードを含むアーカイブ一式はこちら:

http://www.ritsumei.ac.jp/se/re/izumilab/lecture/15Nexys4UartVivado.zip

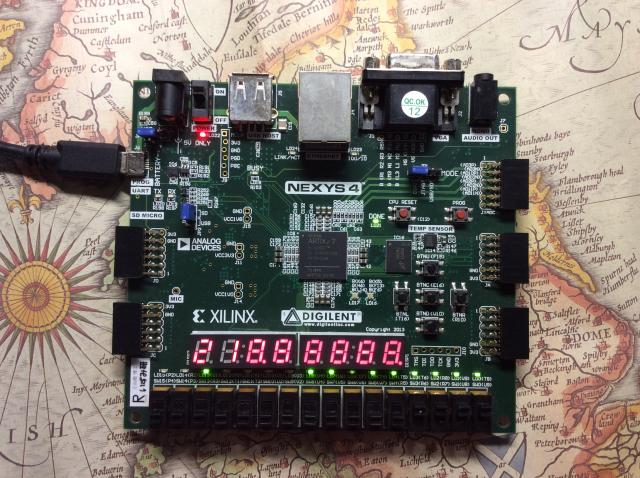

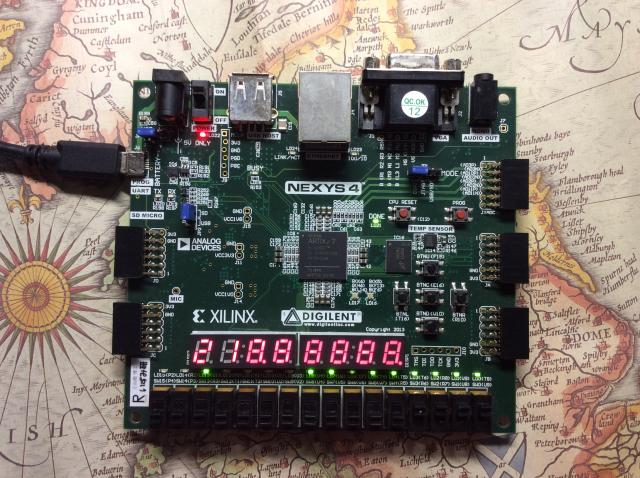

- ターゲットボード

- Nexys-4

- ターゲットFPGA

- XC7A100T-1CSG324C

- (他のボードでトライする場合は、ボードの仕様に合わせてxdcファイルとトップ記述を書き換える)

- 開発環境

- Xilinx Vivado 2015.2

- ※バージョンは 2014.?, 2015.? であれば詳細は異なってもほぼ同じように設計できるはず

- この課題の習得項目は次のとおり。

- Vivado の基本操作、シミュレーション、コンパイル、コンフィグ、実機デバッグ

- Nexys-4 の取り扱い

- コンフィギュレーション方法(直接、PROM書き込み、USBメモリ)

- この課題は次の項目を修得済みの者を対象とする。

- Verilog 記述、シミュレーション

- TeraTerm 等によるシリアル通信

- この課題終了後には次の課題を推奨する。

- 以下、特に指定の無い項目は規定値(デフォルト、最初から入っている値)を設定する。

0. 準備

- Vivado のインストール、ライセンスファイルの登録、ライセンスキーのセット

- TeraTerm等シリアル接続で通信できる端末エミュレータをインストールしておく。

- Nexys4をPCに接続し、電源投入、ドライバ等をインストールしておく。

- Vivado は深くフォルダを掘ってトラブルを起こすので、

課題を実行するフォルダにドライブ文字を割り当てておくとよい。

subst_dir.bat のフォルダ名を変更して実行すると良い。

1. プロジェクトの生成 Vivado

- Vivado を起動する。

既存のプロジェクトが開いていたら [File] -> [Close Project] する。

1-1. プロジェクト生成 (Vivado)

※次回からは、作業ディレクトリ内の nexys4test.xpr をダブルクリックすると Vivado でこのプロジェクトが起動する。

1-2. 画面の確認

- 左側 Flow Navigator (A)で、大まかに何をするか指定する。

- 右側 (B)で、各種設定、操作指示、ファイル編集、などを行う。

- 下側 (C)で、ログや状況の確認を行う。

- 見たい画面が行方不明なときのチェックリスト

- それぞれの領域のタブ(矢印の先)で切り替える

- (A)Flow Navigator で対象手順を選択

- (B1)対象のファイル、モジュール、信号などを選択

- メインメニューの Window(上端の赤矢印)で選択

1-3. ソースファイルの登録

- 上端メインメニュー File, Add Sources を選択。

- (*) Add or create constraints を選択。

- +を押下、Add Files を実行、Nexys4.xdc, debug.xdc を登録。

(注意:対象ディレクトリ(フォルダ)を確認すること!)

- 同様に、上端メインメニュー File, Add Sources を選択。

- (*) Add or create design sources を選択。

- +を押下、Add Files を実行、Nexys4_top.v, hexilum.v, uart.vを登録。(Nexys4_tb.v 以外!)

- 同様に、上端メインメニュー File, Add Sources を選択。

- (*) Add or create simulation sources を選択。

- +を押下、Add Files を実行、Nexys4_tb.v を登録。

- (B1)領域で Sources タブを選ぶ。

- Constraints の中の debug.xdc を右クリックし Set as Target constraint file する(以後の作業で生じた制約・指示類はここに書きこまれる)

- Design Sources の中に登録したモジュール(Nexys4_tb以外)があることを確認する。

- Nexys4_top がトップ(太字)になっていることを確認する。

そうなっていなかったら、Nexys4_topを右クリックして Set as Top する。

(※ここにNexys4_tbが入っていたら先の登録ミス)

- Constraints の中に Nexys4.xdc があることを確認する。

- Simulation Sources の中に Nexys4_tb ほかのモジュールがあることを確認する。

- それぞれのモジュールやファイルをダブルクリックすると

(B3)ウィンドウにファイルが表示されることを確認する。

そこで編集や保存もできる。

2. シミュレーション

- Flow Navigator領域内、Simulation の Run Simulation を選択、Run Behavioral Simulation を実行。

- 右側にシミュレーション画面が現れるのを確認。左から、モジュール階層選択(画面A: Scopes)、信号選択(画面B: Objects)、波形(恐らくUntitled 1)。

- (画面A) Scopes で fpga を選択、(画面B) Objects で rstn を選択、右クリック、Add to Wave Window する。同様に counter を追加する。counter は右クリック Radix で16進数(Hexadecimal)にしておく。

- 上部(画面C)メニューボタンから Restart(|に左三角ふたつ、念のため)を押下して、Run All (右向き三角にデジタル波形マーク)を押下実行。

- 右側にソースコードが表示され $finish に到達して終了する。

- 右側で波形タブを選択し波形を表示する。

- 波形(画面D)左側 Zoom Fit(虫眼鏡に四角)で全波形表示、確認。

- 波形上をクリック、ドラッグ、左側の虫眼鏡+とーを使用して、以下を確認する。

- CLK100MHz が10ns周期で振動。

- 100ns付近で BTNCPURST が0になり200ns 付近で1になる。

- 2760ns、rstn 立ち上がる。counter がカウントアップを始める。

- 3250ns付近から SW の値が 0, 1, 2, 3 ... と変化し、LEDの値が0, 1, 3, 7 ... と変化。

- メインメニュー File → Save Waveform Configuration As を選択、名前を付けて保存。例:Nexys4_tb_behav.wcfg

- 注意…ソースコードを書き変えたら左側 Flow Navigagor 内 Run Simulation をやり直すこと。

3. 実機デバッグの準備

実機デバッグでは、いったん論理合成を通してから、

観測したい信号やレジスタをマークし、

さらにデバッグ用のモジュールを設定登録する。

そして、再合成する。

3-1. 観測対象のマーク

- ソースコード中にデバッグの観測対象を予めマークしておく。

wire/reg の宣言の前に

(* mark_debug = "true" *)

を入れる。

- Flow Navigator(画面A)内、Project Manager を選択

- Sources領域(画面B1)内、Nexys4_top.v をダブルクリック

- メイン画面(画面B3)で counter, uartrxdata, uartrxvalid, uartrxwait,

uarttxdata, uarttxvalid, uarttxwait

のマークを確認

3-2. 論理合成

- Flow Navigator(画面A)内、Synthesis の Run Syntehsis を選択、実行。

- 終了したら、View Reports。

3-3. デバッグモジュールの設定と観測信号の登録

- Flow Navigator(画面A)内、Synthesis → Sysnthesized Design

- 表示レイアウト(下図の☆の箇所)をDebugに設定。

- (画面C)にマークした信号が表示されていることを確認。

-

注意…

ここで(画面B1)Netlistから信号やレジスタを右クリックして Mark Debug することもできる。しかし、ソースコード中の信号やレジスタは論理合成の最適化により名前が代わったり、縮退して消えてしまったりする。

また、

xdc ファイルの中で set_property MARK_DEBUG true [get_nets {uartrx/datao[*]}] などとすると予めマークできそうなものだが、それでも信号&名前の保存は保証されないようだ。

- Flow Navigator (A) から Synthesis → Synthesized Design → Set Up Debug を選択、実行

- Nets to Debug ですべての信号を選択(デフォルト設定のまま)

- ILA Core Options で [*] Capture Control をチェック

- Finish

- メインメニュー File → Save Constraints して保存

- Flow Navigator (A) から Project Manager を選択、Sources の Constraints の中の debug.xdc に追記されていることを確認。

4. コンパイル

- Flow Navigator領域内、Synthesis の Run Syntehsis を選択、実行。

- Flow Navigator領域内、Implementation の Run Implementation を選択、実行。

- Flow Navigator領域内、Program and Debug の Generate Bitstream を選択、実行。

- 各段階でProject Navigator 領域の右上 Project Summary, 下 Messages, Log, Reports などを確認。

- 必要に応じて、ファイルを編集し再実行。Flow Navigator 領域内左上 Sources でソースファイルを選択し開いて、左上で編集・保存する。

5. コンフィグレーション

以下 4a, 4b, 4c 何れかの方法でコンフィグレーションする。

5a. 直接コンフィグレーション

- FPGA を直接コンフィグレーションする。手軽で速いが電源を切ると消える。

- Flow Navigator 領域内、Program and Debug → Hardware Manager → Open Target → Open New Targetを実行、Local server から選択

- Flow Navigator 領域内、Program and Debug → Hardware Manager → Program Device → xc7a100t_0 を選択

- 動作を確認

5b. USB メモリに書き込む

- USB メモリ(or uSD card)に書き込み起動。ケーブル不要、電源投入で自動コンフィグ。

- Nexys4. FPGA Board Reference Manual の 2.3 USB Host and Micro SD Programming を参照すること。

- PC で bit ファイルを USB メモリ(or uSD card)に書き込む。フォーマットはFAT32で、トップにひとつだけ書き込むこと。

- ボードの JP1, JP2 を USB モードに設定しておく。

- USBメモリをボードに挿し、PROGボタン押下あるいはボード再起動。

5c. オンボード FLASH ROM に書き込む。

オンボードオンボード FLASH ROM に書き込む。手間と時間はかかるが、電源投入に自動コンフィグ。

bin file を生成する方法

mcs file を生成する方法

- xdc ファイルに次を記述する。

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

set_property CONFIG_MODE SPIx4 [current_design]

- 下部画面 Tcl Console で以下のコマンドを実行する。(注 -size は MBytes で指定するので 128Mbit -> -size 16)

# write_cfgmem -format mcs -interface SPIx4 -size 16 -loadbit "up 0x0 ./nexys4test.runs/impl_1/Nexys4_top.bit" -file Nexys4_top.mcs

- Hardware Manager で Mempry Part は s25fl128sxxxxxx0-spi-x1_x2_x4 を指定して書き込む。または Tcl Console で以下のコマンドを実行する。

# program_flash -f Nexys4_top.mcs -flash_type s25fl128sxxxxxx0-spi-x1_x2_x4 -verify -cable type xilinx_tcf url tcp:localhost:3121

6. 実機実行と動作確認

以下の動作を確認する。

以下の動作を確認する。

- 16bit LED と 16bit Slide SW

- SW を全1にする→ 16bit LED がカウントアップ

- SW を全0にする→ 16bit LED が全消灯

- SW を1,2,3...7(二進数)にする→ 16bit LED が右から1,2,3...7個点灯。

- UART

- PC と Nexys-4 を接続する。

- PC で端末エミュレータを立ち上げ、シリアル接続する。設定は 115200bps, 8bit, no parity, 1 stop bit, no flow control

- PC から文字を送ると、大文字⇔小文字変換されて帰ってくる。

- 1文字送受するたびRGBランプが変化する

- 7seg LED

- 通常は、上位にカウンタ値、下位にスライドスイッチの値(16進数)、

点にプッシュボタンの値。

- 中央ボタン押下で、上位から、UART 送信文字数、送信文字、受信文字数、受信文字、点に送受信データ制御信号。

7. 実機デバッグ

7-1. コンフィギュレーション

- FPGA を直接コンフィグレーションする。手軽で速いが電源を切ると消える。

- Flow Navigator 領域内、Program and Debug → Hardware Manager → Open Target → Open New Targetを実行、Local server から選択

- Flow Navigator 領域内、Program and Debug → Hardware Manager → Program Device → xc7a100t_0

7-2. 観測条件の設定

- Hadware Manager (画面B1) 内 hw_ila_1 を選択

- Setting - hw_ila_1 (画面B3a) 内 Capture mode: BASIC, Trigger position in window: 512 (窓サイズ1024の中央)にする。

- Trigger Setup - hw_ila_1 (画面B3c) 内で+(トリガ追加)し、BTNC_reg を追加

- BTNC_reg の Compare Value を Operator: ==, Radix: [B], Value: R にする。

- 同じくトリガに uartrxdataを追加し

Operator: ==, Radix: [H], Value: 40 にする。

- Trigger Setup - hw_ila_1 (画面B3c) 内の右下の論理ゲートマーク(虫眼鏡、プラス、マイナスの下)を押し、Set Trigger Condition to 'Global OR' を選択。

- メインメニュー File → Save Waveform Configuration As で設定を保存

7-3. 信号の観測(1)

- Status - hw_ila_1 (画面B3b) 内 の実行ボタン(右向き三角に縦棒)を押す

- トリガ待ち状態になる

- Nexys-4 ボードの BTNC を押下する

- 観測信号がボードから読み出される

- Waveform - hw_ila_1 (画面B3e) 内 の全体表示ボタン(四角の枠で囲まれた虫眼鏡)を押す

- 波形画面の中央(時刻512)で BTNC_reg が立ち上がっているのを確認

- Waveform - hw_ila_1 内 (画面B3e) の拡大ボタン(虫眼鏡に+)を何度か押して、counter が増加しているのを確認

- 拡大/縮小や表示位置移動などの使い方をマスターしておく

7-4. 信号の観測(2)

- PCの端末エミュレータ(TeraTerm等)でNexys-4ボードととUART接続

- Status - hw_ila_1 内 の実行ボタン(右向き三角に縦棒)を押す

- PCの端末エミュレータから abc@xyz と入力

- @(文字コード0x40)を入力したところでトリガがかかり、観測信号がボードから読み出される

- トリガポイント(時刻512)付近を拡大

- uartrxvalid, uartrxwait 信号が所望の動作をしていること確認

99. その他

Verilog デバグ〜埋もれたタイプミスを見つける

Verilog では、信号を宣言せずに使用してもよい。

なので、タイプミスをしてもエラーにならない。

そのようなバグを見つけるためには、

Messages から次の Warning を検索して確認するとよい。

- [Synth 8-3331] unconnected port

- [Synth 8-3848] does not have driver

- [Synth 8-3295] tying undriven pin to constant

Windows の COM ポート番号について

Windows は接続したことのあるデバイスを覚えていて、

COM ポート番号を使いまわす。

そのため、新しいデバイスを接続するたびにポート番号が増えていく。

ツールによっては COM ポートの番号が一桁でなければ正常動作しないものがある。

番号を振り直すには、不使用ポートを削除して接続し直す。

- コンピュータのプロパティから詳細設定、環境変数の設定で DEVMGR_SHOW_NONPRESENT_DEVICES を 1 に設定する。

- デバイスマネージャを起動、表示→非表示のデバイスを表示

不要なポートを削除。