マイクロマシン集積チップサービス

MICS (Micromachined Integrated Chip Service)

サーフィスマイクロマシン

試作サービス

SURF-MICS

アナログIC試作サービス

AIC-MICS

LIGAプロセスを用いた

試作サービス

LIGA-MICS

MICSとは?

■マイクロマシンの研究者が協同して,高度半導体ICプロセス技術を有するファウンドリに委託し,最高水準のマイクロマシンを低コストで試作するためのサービスです。現在,3層ポリシリコン構造の試作を行うサーフェスマイクロマシン試作サービス(SURF-MICS)と1.6μm-Bi-CMOS 1000 素子規模で高性能オペアンプ9個分を内蔵するアナログIC試作サービス(AIC-MICS)の2つのサービスを提供しています(LIGAプロセスを用いた試作サービス(LIGA-MICS)は準備中です)。

■MICSのデザインフローは,右の図に示すとおりです。

- ユーザは,ファウンドリより提示された設計基準に従いチップのパターン設計(マスク設計)を行います。設計データは,標準フォーマットでマスクメーカに送られます。

- マスクメーカは,各ユーザの設計した複数種類のチップをレイアウトしフォトマスクを製作します。

- ファウンドリは,マスクメーカが製作したフォトマスクを受け取り,Si ウエハにプロセス処理を行います。

- 完成した Si ウエハは,ダイシングされ,チップに分割されます。個々のチップは,各ユーザに配給されます。

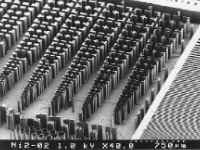

■サーフェスマイクロマシン試作サービス(SURF-MICS)

SURF-MICSの構造は,犠牲層サーフェスマイクロマシニング3層ポリシリコン構造です。犠牲層には,PSGを使用しています。プロセスは,3層ポリシリコンのサーフェスマイクロマシニングのために特別に調整されており,可能な限り多くのユーザが利用できるように設計されています。

■アナログIC試作サービス(AIC-MICS)

AIC-MICSは,マイクロマシン周辺回路用アナログASICです。プロセスは1.6μm-Bi-CMOS,1000素子規模で標準的なオペアンプ9個分が入っています。設計は,マスタースライス方式で2層の Al 配線およびスルーホールの計3層を設計します。設計データは,GDS-Ⅱなどのマスクデザインの標準フォーマットで提出します。