|

|

硫化法を用いたCIS系太陽電池の作製

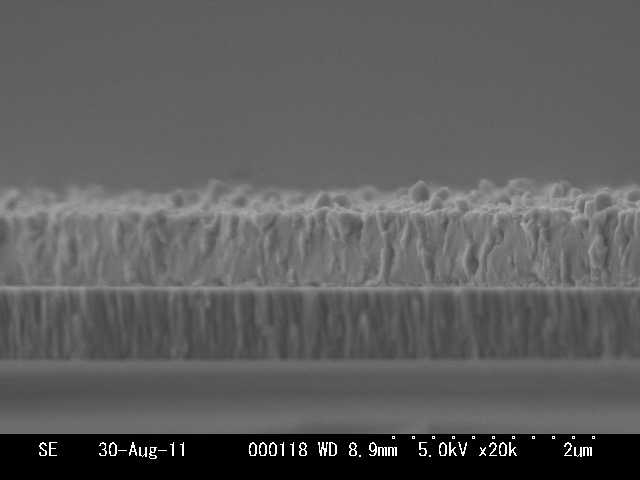

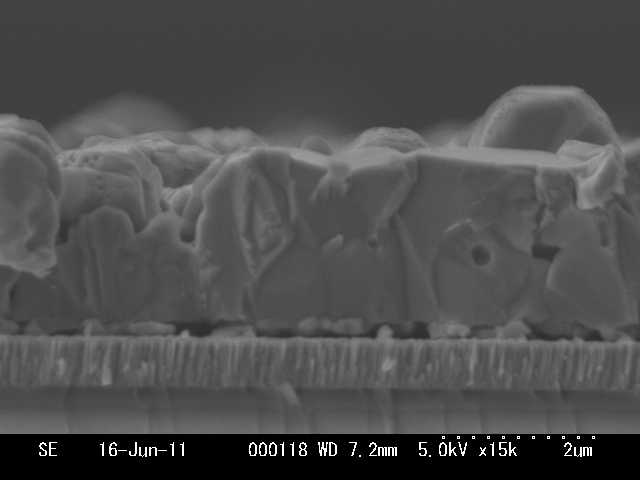

CuInS2(CIS)化合物半導体は禁制帯幅Egが1.53eVであり、太陽電池にとって最適なEg=1.4eVに近く高変換効率が期待されている。 しかし、現状では最高変換効率が12%程度と理論よりも効率が低い。 この原因としてCu過剰組成で結晶成長を行ったCIS膜の表面ラフネスが大きいことが考えられる。 これにより、表面積増加や太陽電池作製の際にCIS上に堆積させるバッファ層のカバレージが不十分となり、開放電圧Vocが低下していると考えられ研究を行っている。

CISの作製方法としては主に蒸着法と硫化法がある。 蒸着法は高真空状態でCu、In、Sそれぞれ単体を蒸発させて基板に照射してCIS薄膜を作製する方法である。 この方法では、高品質な結晶が得られやすく、12.2%の変換効率が達成されている。 しかし、設備投資コストや大面積化の点から近年では硫化法を用いたCIS薄膜の作製が主流となっている。 硫化法はCu-In積層膜やCu-In合金膜をH2Sガス雰囲気またはS蒸気雰囲気にて500oC程度の温度で熱処理することでCIS薄膜を作製する方法である。 この方法では、Cu-In前駆体の膜の作製が容易であり、組成制御も膜厚で制御できる。 また、スパッタリング法を用いると大面積化も容易である。 実際この方法も用いて、変換効率11.4%が達成されている。

また、CISベースの半導体はCISeベースの半導体よりワイドギャップな太陽電池を作製できるため、次世代太陽電池として注目されているフルスペクトル太陽電池のトップセル層としての応用が期待されている。