トップ プロフィール 研究内容 卒業研究 連絡先 業績 リンク集

電気電子工学科今井研究室の卒業研究の紹介

研究テーマ:単電子デバイスの理論的研究

| 1950年代に誕生した集積回路は、回路を構成する部品を微細化することにより発展してきた。今日の集積回路を構成しているMOS型トランジスタは、 スケーリング則(比例縮小則)に基づいて微細化され、現在ゲート長は数十nmに至るまで縮小した。微細化により集積回路の高集積化のみならず、高速化、低消費電力化も実現してきた。 今日、情報量の飛躍的増大や携帯化に対応してさらに高集積化、低消費電力化を推進することが要請されている。しかし、微細化がこのまま進行すれば、電子数の統計的揺らぎの増大、 トンネル効果等の量子力学的効果の顕在化等の物理的原理的限界に突き当たる。従って、従来のようにスケーリング則に基づく微細化を行うだけでなく、新しい材料やトランジスタ構造、 動作原理を導入していく必要がある。単電子デバイスはこのような要請に応える新しい動作原理に基づく極微細デバイスであり、名前の通り電子を1個ずつ制御する。電子1個を1ビット の情報に対応させれば、低消費電力化を極限まで推し進めることができる。今井研究室では、この単電子デバイスの理論的研究をテーマにしている |

|

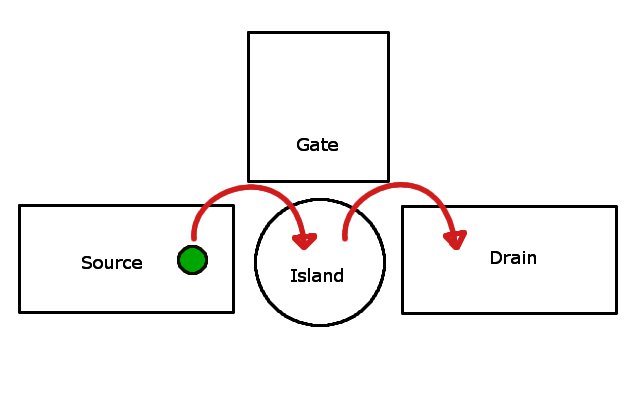

図1のようにソース電極とドレイン電極の間に極微細な導電領域(島と呼ばれる)を作る。 ソース電極・ドレイン電極と島は非常に薄い絶縁体により隔てられており、電子はトンネル効果により島を出入りすることができる。 もし電子が移動すると元の場所には正電荷が取り残されるが、これは負電荷を有する電子と互いに引き合うので、実際に電子の移動を行うにはこの引力に打ち克つ力が必要である 。また、2個の電子は電気力により互いに反発し合うため、2個の電子が極微細な島内に存在するためには高いエネルギーが必要である。 このような効果を利用することにより電子を1個1個制御する素子を単電子デバイスと呼ぶ。 単電子デバイスでの電子移動の制御は、島の近傍に配置されたゲートと呼ばれる電極に電圧を印加することにより行う。 単電子デバイスには、単電子トランジスタ、単電子ターンスタイル、単電子ポンプなどの種類がありそれぞれ異なる動作を行う。 |

図1 単電子トランジスタ (Single Electron Transistor) |

|

電子のもつ熱運動のエネルギーが電子間の反発力により生じるエネルギーより大きいと単電子

デバイスは正常に動作することはできない。そのため、単電子デバイスが室温で動作するには、数nm

の極微細な構造が必要である。従来提案されている様々な単電子デバイスでは、極微細なゲートを特定の島の近傍に配置するが、

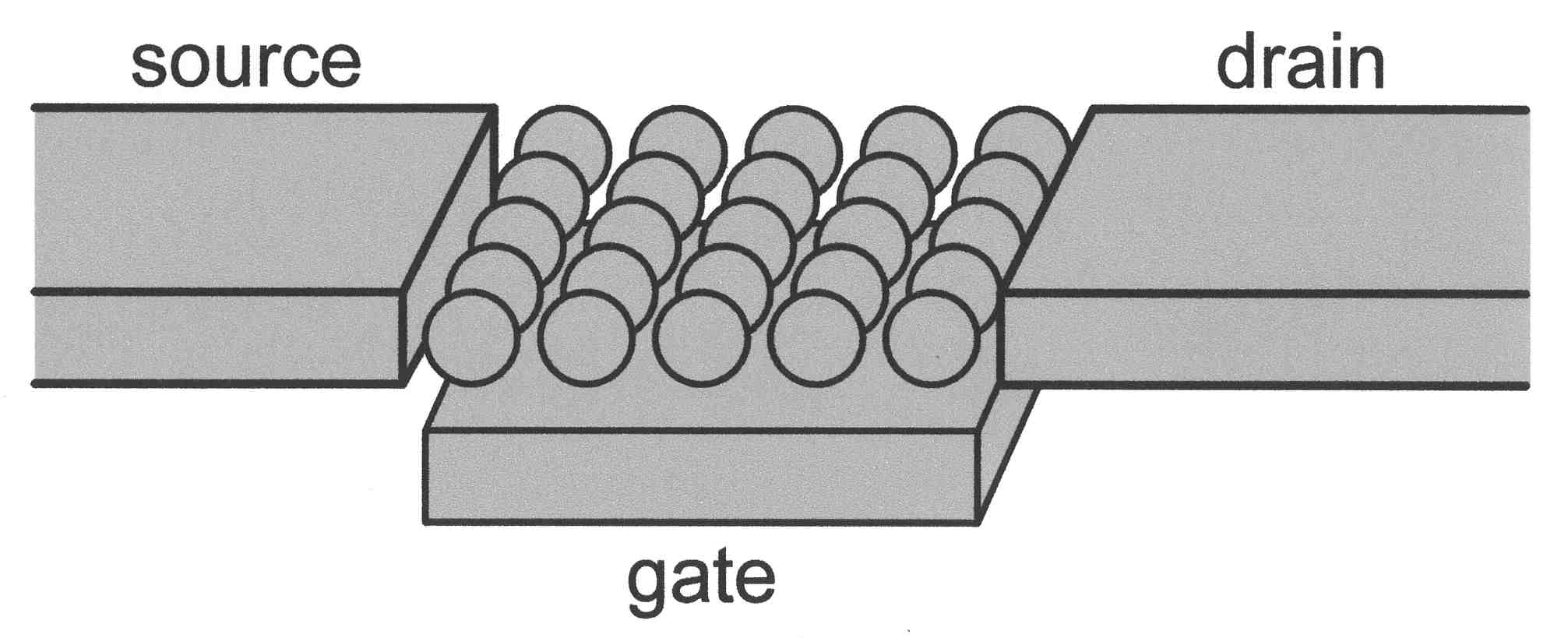

このような極微細構造は簡単に作製することができない。しかし、実際には図2に示すような

多重ドット共通ゲート構造でも単電子デバイスが実現することが明らかになっている。

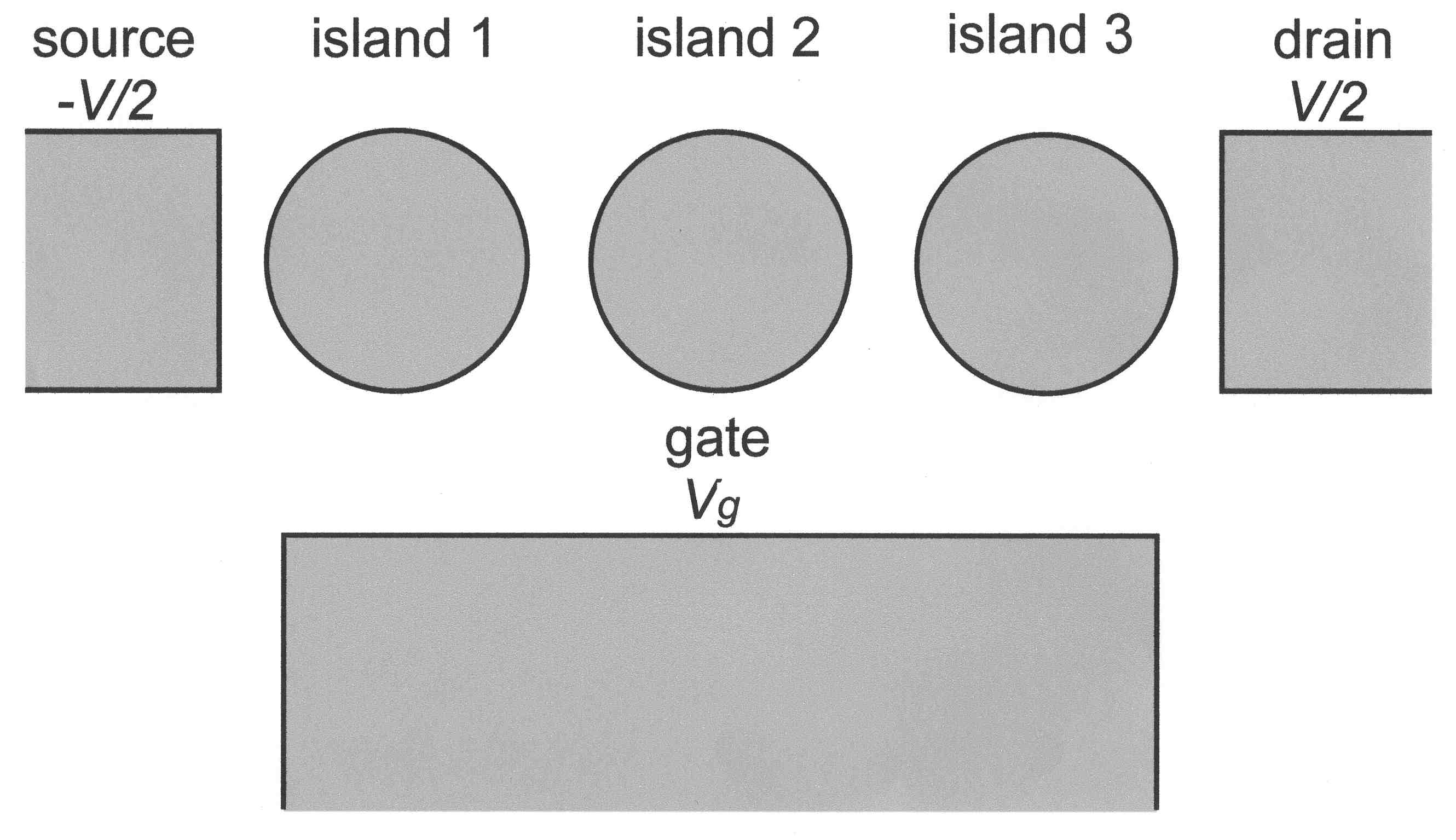

そこで、今井研究室では、図3に示すように島の数が2個から4個程度の共通ゲート構造を取り扱っている。

図3の構造は、共通ゲート構造なので容易に作製することができ、島の個数が比較的少ないので、理論的な取扱いも容易である。

島の個数や配置を変えることにより実現する新構造の単電子デバイスの動作を明らかにすることを目的に理論計算による研究を行っている。

デバイスの動作条件を求めるために、等価回路モデルを用いてデバイス内部の実効容量や電位分布を代数的に計算し、

それを基に電子移動が許されるか否かを判断する。この手法により、これまで、2個の島を有する単電子デバイスは

内部構造がたとえ不均一でも単電子トランジスタ(電子が1個ずつ島を通過することにより電流が流れる)として動作すること、

3個の島を有する内部構造が左右対称な単電子デバイス、または4個の島を有する内部構造が均一な単電子デバイスは

単電子ターンスタイル(ゲート電圧の上げ下げにより単電子を転送する)として動作することを明らかにした。

また、デバイスの動作条件を詳細に明らかにしてきた。今後は以下の場合について調べていく予定である。

① 二重ドット単電子トランジスタ 2つの島の配置が直列でない場合の動作条件を調べる。 ② 三重ドット単電子ターンスタイル 構造が左右非対称である場合の動作条件を調べる。 ③ 四重ドット単電子ターンスタイル 構造が左右対称だが不均一である場合の動作条件を調べる。 ④ 温度の影響、電流の計算 これまでは絶対零度の場合の動作条件を調べてきた。電子の熱運動の影響を考慮した場合についても調べ、電流の大きさや単電子転送の確率も調べる。 ⑤ 単電子インバータ CMOSインバータと類似した回路構造の単電子インバータの動作を構造が一体のものとして解析を行う。 |

図2 共通ゲート構造 | |

| |

図3 共通ゲート三重ドットデバイス |

|

毎週、院生とともにミーティングを行い、各メンバーの研究紹介や報告を行う。

また、ゼミ(テキストの例は下記[1]~[5])を行い、単電子デバイスについての理解を深める。また、前期

には単電子デバイスに関する初歩的な計算演習も行う。研究テーマは前期の早い時期に設定する。

研究は、ウエストウイング・4階の電子デバイス第1第2研究室において行っている。

|

■テキストの例

[1] Rainer Waser Ed., Nanoelectronics and Information Technology.

[2] Zahid Ali Khan Durrani, Single-Electron Devices and Circuits in Silicon.

[3] 榊裕之,横山直樹共編,ナノエレクトロニクス.

[4] 平本俊郎編,集積ナノデバイス.

[5] 勝本信吾,メゾスコピック系.

戻る