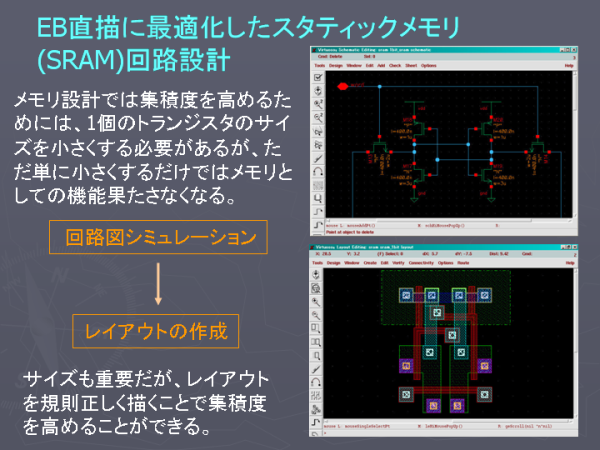

■EB直描に最適化したスタティックメモリ(SRAM)回路設計

研究者氏名:

下村 弘

研究内容図面紹介

研究の感想:

初めてのことだらけで大変ですが、回路図 → レイアウト → チップ の課程を自分で行うので、

実際にチップが作るということが体験でき、いろいろな発見があるのでやりがいがあり面白いです。

下村 弘

研究内容:

SRAMは、消費電力が小さく動作が速いですが、CMOSでは6個のトランジスタを用います。

SRAMの1bitメモリセルやセンスアンプは多くの参考書で紹介されていますが、周辺回路などはあまり紹介されていないため、

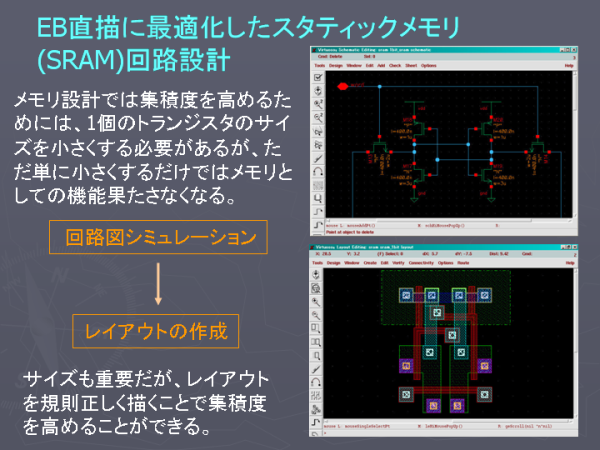

回路構成を調べ、hspiceを用いて波形を入力し、シュミレーションしてCMOSの幅や長さを調べ、

Rohm0.35umのデザインルールにあわせた最適なレイアウトを描き回路図と照合などをし、

最終的にチップレベルにまでもっていくことが目的です。

研究内容図面紹介

初めてのことだらけで大変ですが、回路図 → レイアウト → チップ の課程を自分で行うので、

実際にチップが作るということが体験でき、いろいろな発見があるのでやりがいがあり面白いです。