研究紹介

大容量のメモリとマイクロプロセッサ等のロジック回路を,1チップの大規模集積回路(VLSI)上に実現した「システムLSI」は,

さまざまな情報機器で使用される「小型低消費電力かつ高性能なシステムの実現」に必須の技術となっています.

確かにLSIの設計CAD技術は非常に進歩しましたが,LSIの仕様が決定したら,ハードウエア記述言語(HDL)で記述し, あとはLSI設計CADを使って簡単にシステムLSIは作成できるというわけではありません.

実際に低消費電力・高性能・低コスト・高信頼性などの要求を満足しようとすると,新しい特徴あるLSIアーキテクチャ&回路が必要となってきます.

当研究室では,以下のような特徴あるLSIアーキテクチャ&回路の研究とセキュリティー関連の応用技術を研究しています.

(1)ビアプログラマブルLSI設計

(2)耐タンパLSI設計&非接触電力転送

(3)マトリックス型超並列プロセッサ開発と応用

(4)製造ばらつきを利用した固有ID生成技術

確かにLSIの設計CAD技術は非常に進歩しましたが,LSIの仕様が決定したら,ハードウエア記述言語(HDL)で記述し, あとはLSI設計CADを使って簡単にシステムLSIは作成できるというわけではありません.

実際に低消費電力・高性能・低コスト・高信頼性などの要求を満足しようとすると,新しい特徴あるLSIアーキテクチャ&回路が必要となってきます.

当研究室では,以下のような特徴あるLSIアーキテクチャ&回路の研究とセキュリティー関連の応用技術を研究しています.

(1)ビアプログラマブルLSI設計

(2)耐タンパLSI設計&非接触電力転送

(3)マトリックス型超並列プロセッサ開発と応用

(4)製造ばらつきを利用した固有ID生成技術

ビアプログラマブルLSI設計

LSI製造工程でビア2〜3層だけを,フォトマスクの不要な電子ビーム描画装置を使ってプログラムすることで,自由に回路論理を変更できるLSI.

ASICで回路論理を変更するために必要な1億円以上のマスクコストを削減でき,「世界で1つしかないLSI」を製造することが可能.

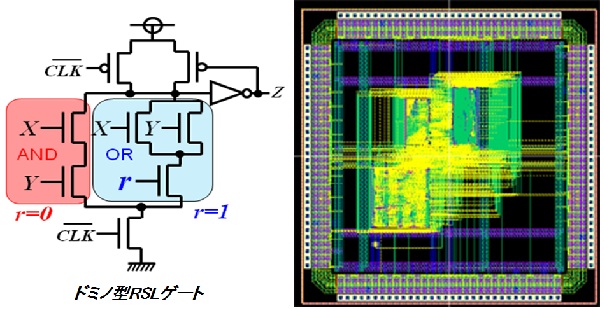

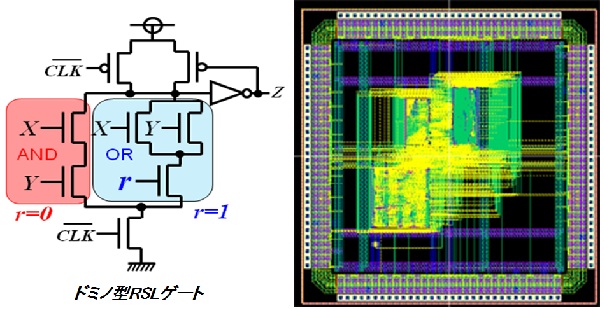

耐タンパLSI設計&非接触電力転送

暗号回路の動作中に,その消費電力をモニタすることで暗号鍵を推定する差分電力解析型サイドチャネルアタックがセキュリティー上脅威となっている.

このような攻撃から暗号回路を守る設計技術が「耐タンパLSI設計」である.当研究室オリジナルの乱数を用いて消費電力を均一化する

ドミノRSL回路を用いたDES暗号回路を設計し耐タンパ性を評価している.

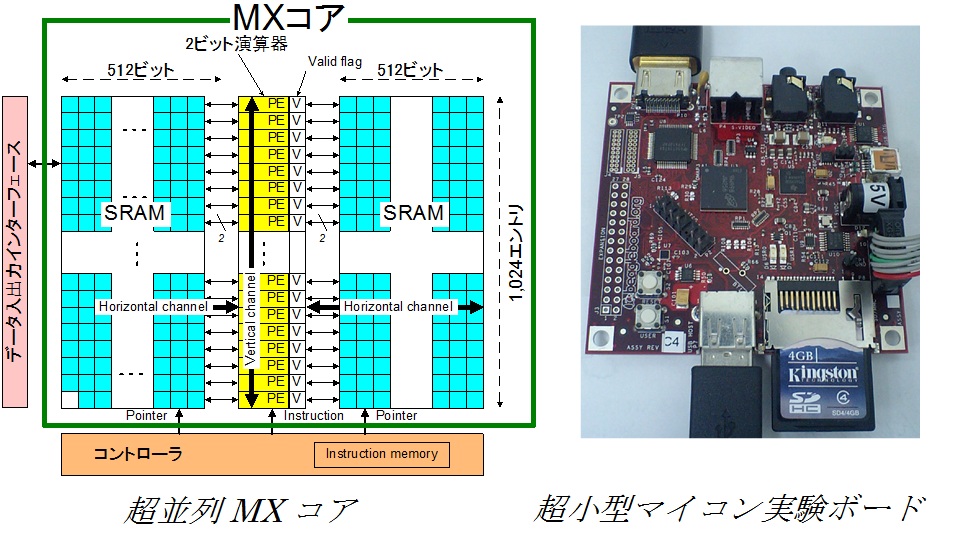

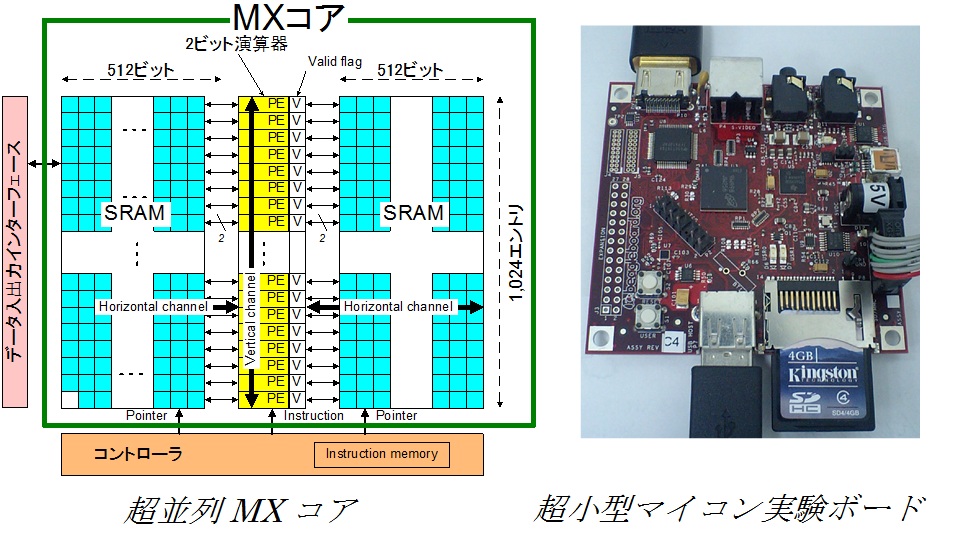

マトリックス型超並列プロセッサ開発と応用

最大1,024並列のデータ処理能力を誇るモバイル機器向けLSIの開発とその応用を行っている.現在は暗号化,乱数生成,物体検出,

及びネットワークアプリケーション等の高速化について研究中.また,超小型マイコンボードを用いたアプリケーション開発も行っている.

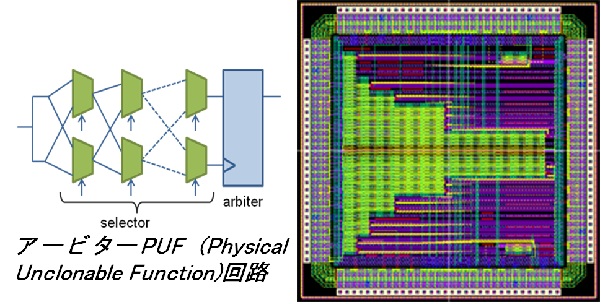

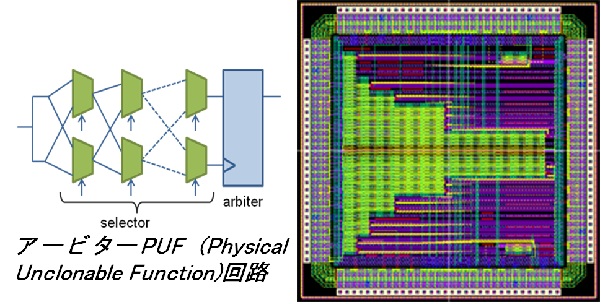

製造ばらつきを利用した固有ID生成技術

ICカードや,LSIなどの付加価値の高いデバイスを複製し不正使用するクローン攻撃を防止するためにはデバイスごとに固有のIDを持たせることが必要である.

当研究室ではトランジスタチェインの伝搬遅延時間の製造ばらつきを利用したアービターPUFを設計し,生成するID再現性とID衝突耐性を評価している.

RFIDの他将来は偽札偽造防止などにも役立つ可能性がある.

研究設備

見出しをクリックすると詳細をご覧いただけます.

研究室インフラ

藤野研の各種インフラ設備.個人PCからネットワークプリンタ,サーバー等があります.

LSI設計環境

ローム記念館のサーバールームには,藤野研専用の8コア搭載のLSI設計サーバー2台と,6TBのファイルサーバを1台設置.試作設計をはじめとした各種LSIの設計,シミュレーションを行うことができます.

実験設備・実験環境(ハード)

実験環境として,導入向けのHDL練習用から試作チップ評価用などの様々なFPGAボード,実際に試作したチップやデバイスなどの実測環境,オシロスコープ,恒温槽など,

LSIのトータルな実験環境を用意しています.

実験・シミュレーション環境(ソフト)

C言語のプログラムや並列処理LSIのプログラミング,Verilogシミュレーションなどによる仮想実験環境など,ソフトウェア面での実験も行うことが出来ます.