機能メモリ回路の設計

研究者氏名:

早崎雅彦

LSIの設計には、機能を記述した後、回路図を得た後、レイアウトを描いた後などの各段階でシミュレーションによって機能、回路の動作、レイアウトパターンを検証します。

小さなミスでエラーが出たり、全く違うモノになったりします。なぜそのエラーが出たかなどを考えて見つけるコトは結構楽しかったりします。時には全く分からなかったりもしますが・・・それも良い経験です。

早崎雅彦

研究内容:

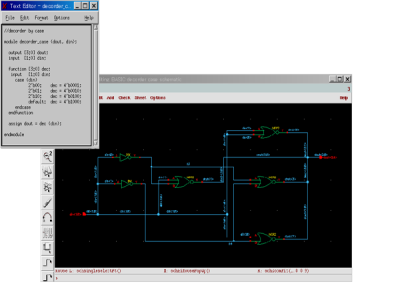

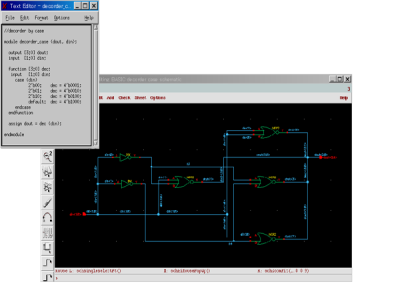

LSIのチップを設計をするには、まず、ハードウェア記述言語verilog-HDLを用いて機能記述をし、シミュレーションして機能を検証します。それを論理合成して、ゲートレベルの構成(回路図)を具体化させ、更に、回路の動作を論理シミュレータで検証します。その回路図を元にレイアウトを描き、検証します。

今は論理合成されたある大規模な回路をHSPICEでシミュレーションしているのですが、回路の規模が大きいため何時間もかかったりしています。図の回路では規模が小さいために時間は全くかかりません。

研究の感想:

LSIの設計には、機能を記述した後、回路図を得た後、レイアウトを描いた後などの各段階でシミュレーションによって機能、回路の動作、レイアウトパターンを検証します。

小さなミスでエラーが出たり、全く違うモノになったりします。なぜそのエラーが出たかなどを考えて見つけるコトは結構楽しかったりします。時には全く分からなかったりもしますが・・・それも良い経験です。