Verilog-HDLを用いたネットワーク機器の設計とFPGAへの実装

研究者氏名:

村井彰信

研究の感想:

研究の感想:

とにかく、プログラムの作成・デバッグの繰り返しですが、FPGAを搭載したボードに実装することで、 実際の動作が目に見えた形で現れるので、思い通りに動作するとちょっと感動ものです。

村井彰信

研究内容:

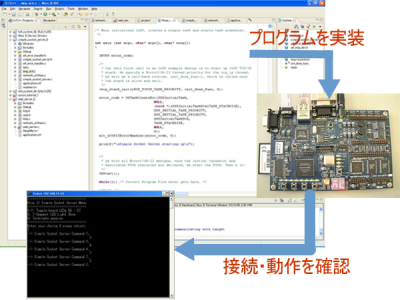

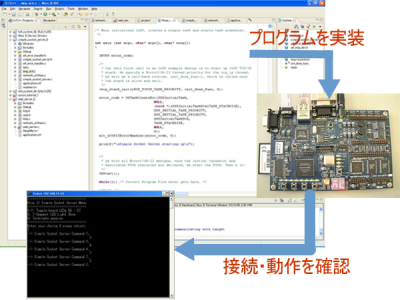

ハードウェア記述言語であるVerilog-HDLでネットワーク機器(まだ決定していませんが)の設計、

シュミレーションを行い、実際に書き換え可能なLSIであるFPGA(Field Programmable Gate Array)に書き込み、

その動作の検証などを行います。

設計段階でのシミュレーションでうまく動作したり、考えどおりの波形を出すことが出来ても、

実際にLSIに実装すると、うまく動作しないこともよくあります。

実現可能なVerilog-HDLプログラムを設計し、動作させることが目標です。

とにかく、プログラムの作成・デバッグの繰り返しですが、FPGAを搭載したボードに実装することで、 実際の動作が目に見えた形で現れるので、思い通りに動作するとちょっと感動ものです。